# SIEMENS

# Geschäftsbereich Basisinformationssysteme

# KUNDENDIENST

Basis-Datensystem 6.000

TECHNICAL MANUAL 6.610

**VOLUME II**

Best.-Nr. D45/50010

# DISKETTE CONTROLLER TDV 2114

# **CONTENTS**

Section Section colour

INTRODUCTION Gold

General

**Recording format**

Signal tables Gold

**HARDWARE**

Input/Output control Emerald

Read mode Rose

Write mode Blue

Internal processor Green

SOFTWARE

Input/Output instructions

Controller m-p instructions Cream

Program flow charts

Program codes Grey

# INTRODUCTION

|                  | Page |

|------------------|------|

| General          | 1    |

| Recording Format | 5    |

| Signal Tables    |      |

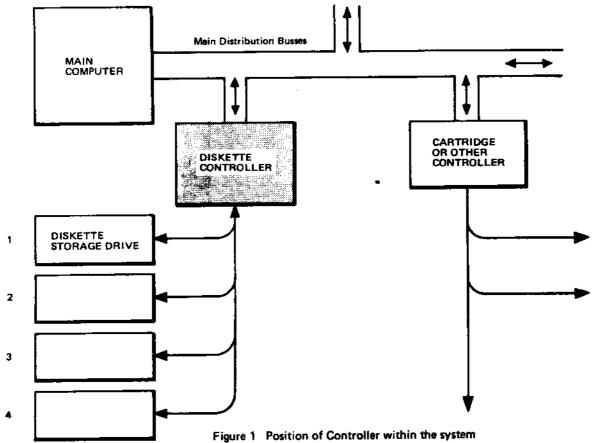

The diskette controller is a separate unit from the diskette storage drive and is the controlling interface between the drive and the main computer, Figure 1.

The system consists of a diskette storage drive which contains the drive mechanism, read/write heads, track positioning mechanism and the removable floppy disk (diskette). The associated control electronics is contained on a printed circuit board within the drive.

When the main computer requires to read data from or write data to a diskette it addresses the controller and transfers the instructions and commands for the particular mode. The controller then selects any one of four diskette drives and prepares the diskette to read or write. Once started, the controller logic is capable of transferring data between the diskette and the main computer memory independently of the main computer program.

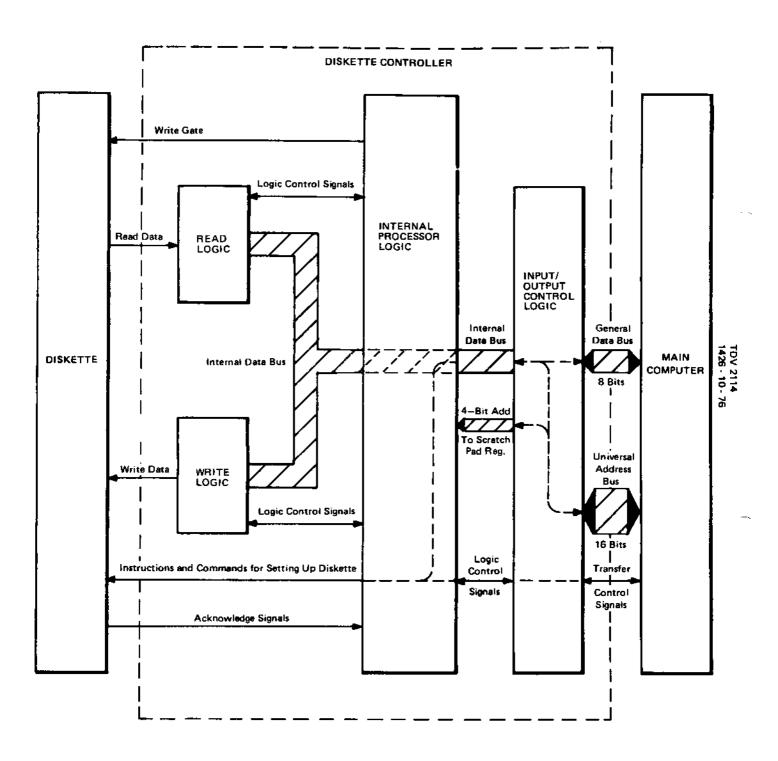

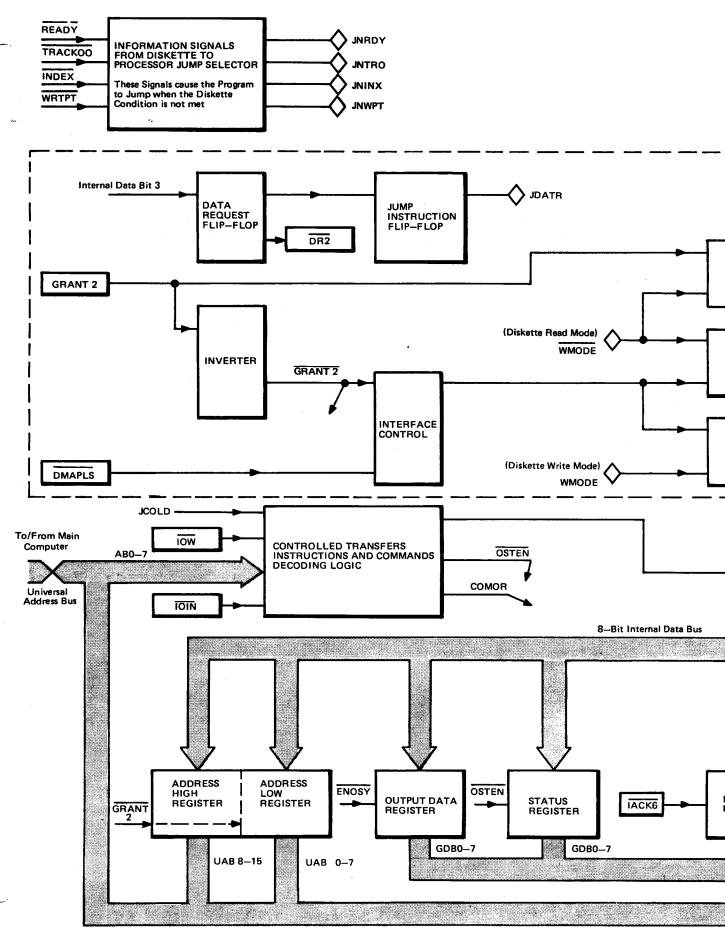

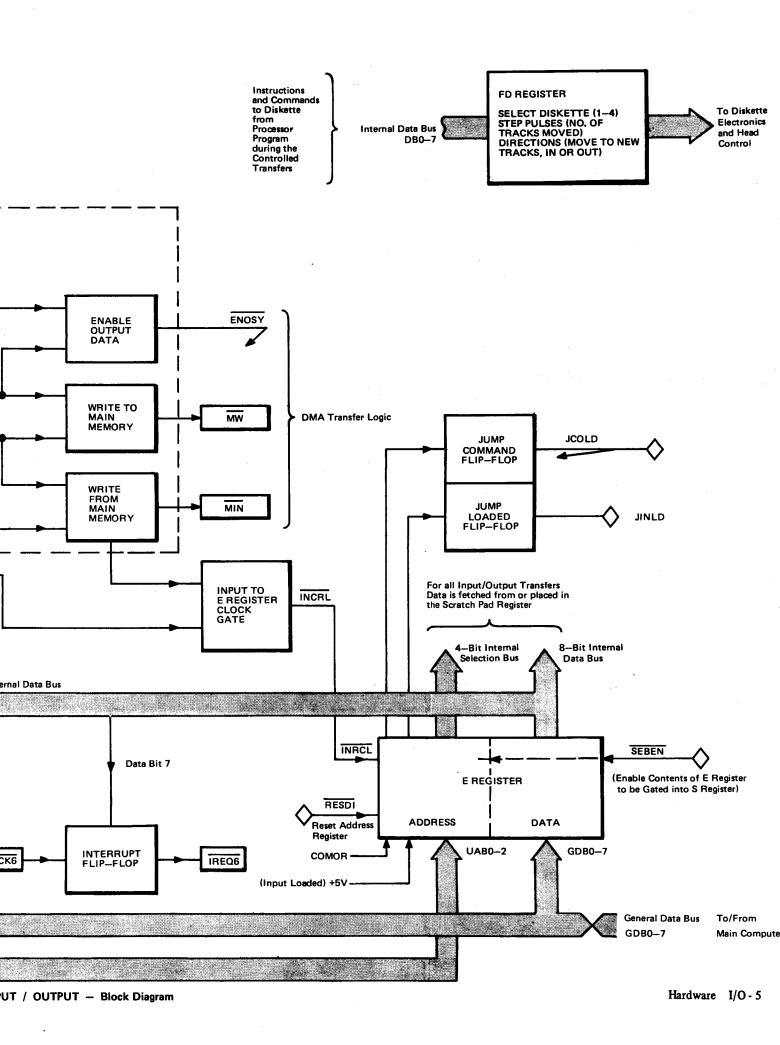

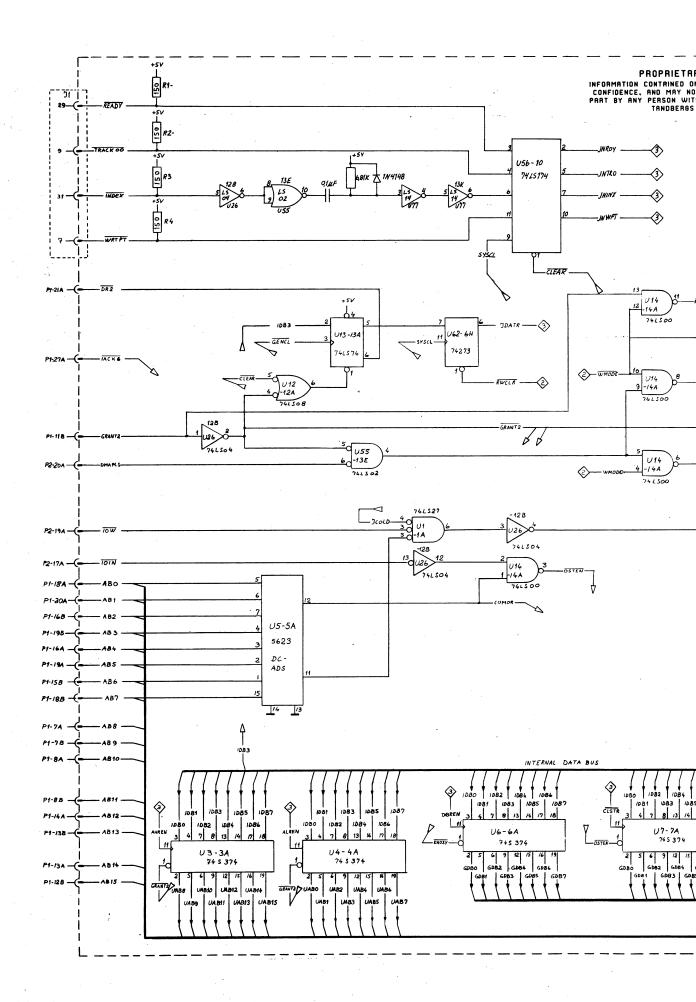

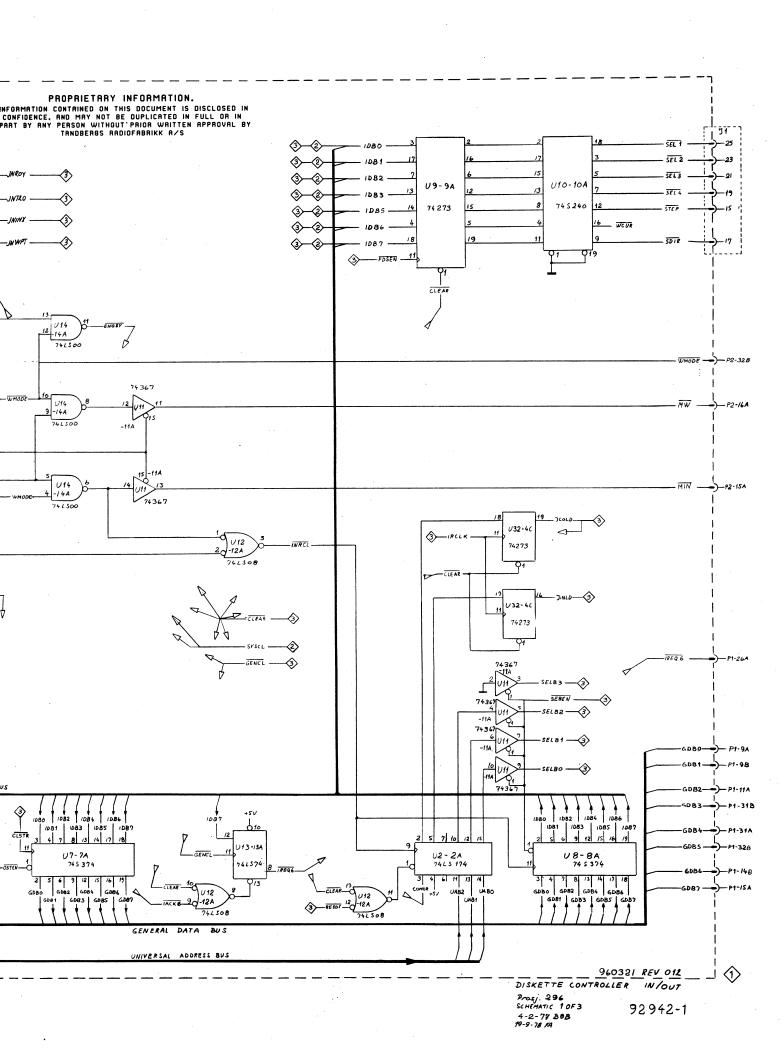

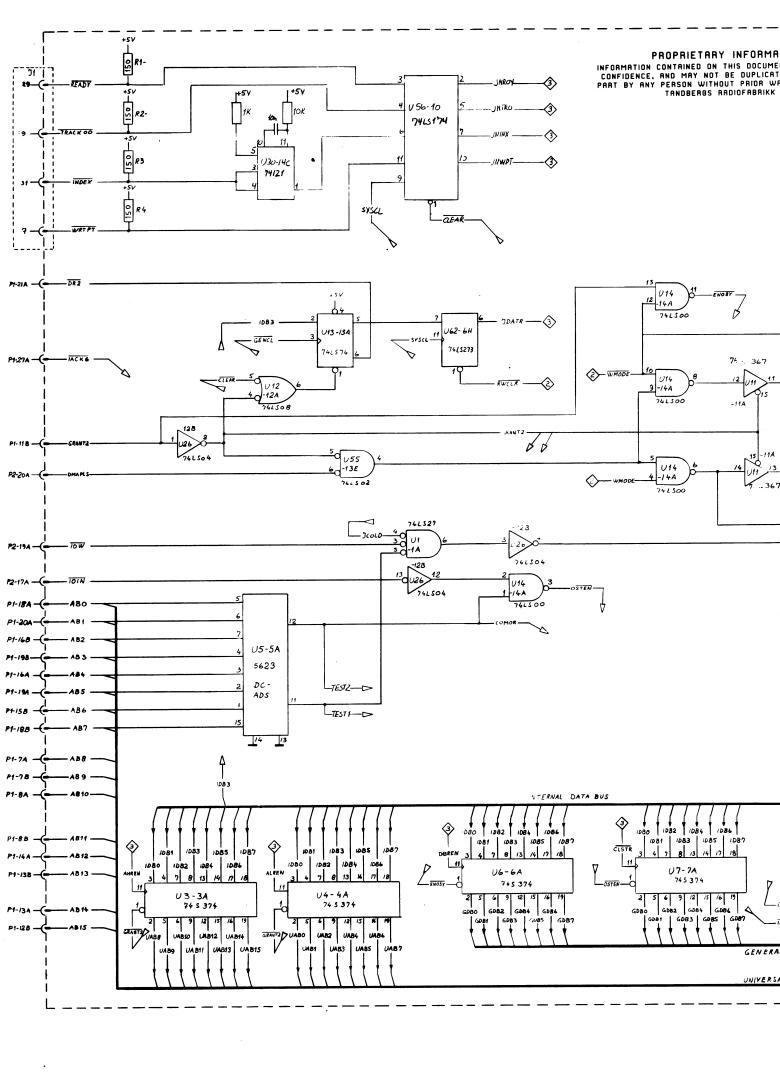

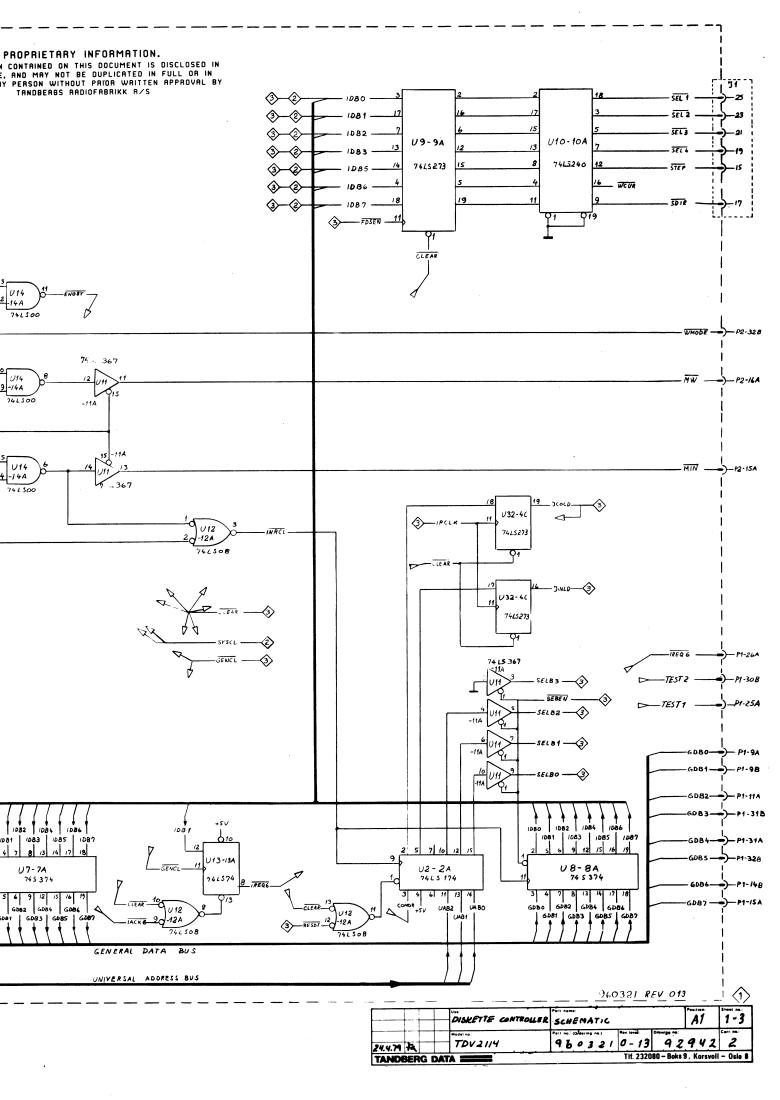

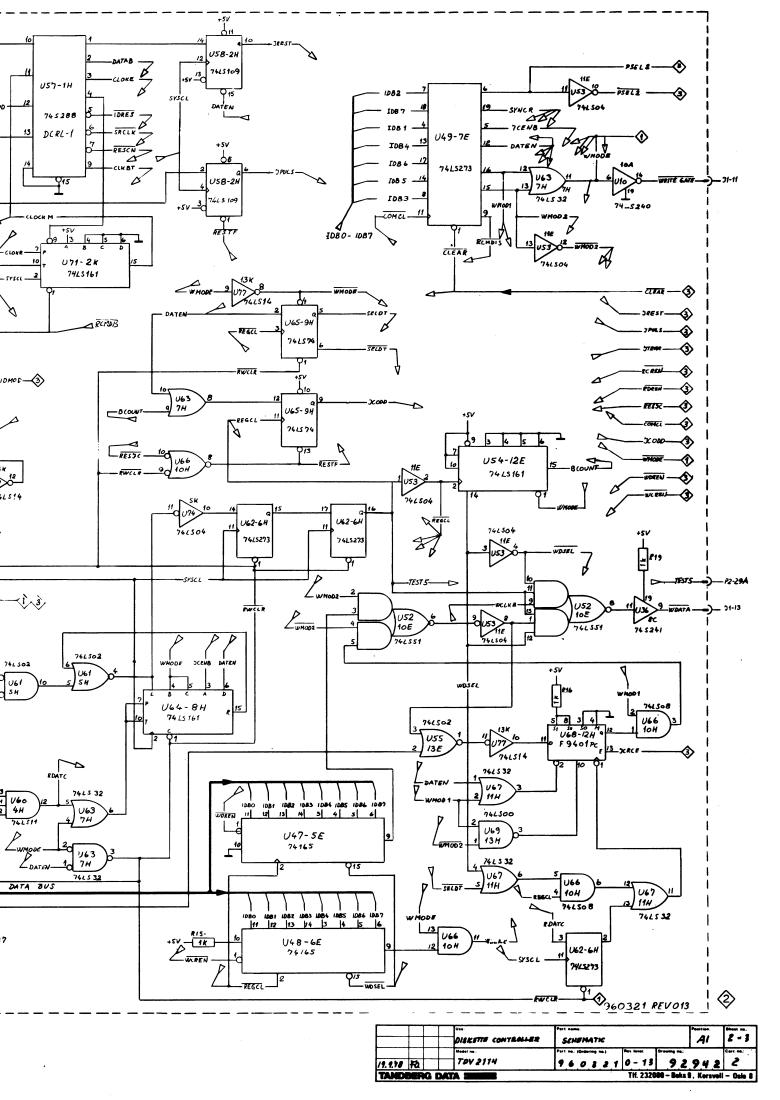

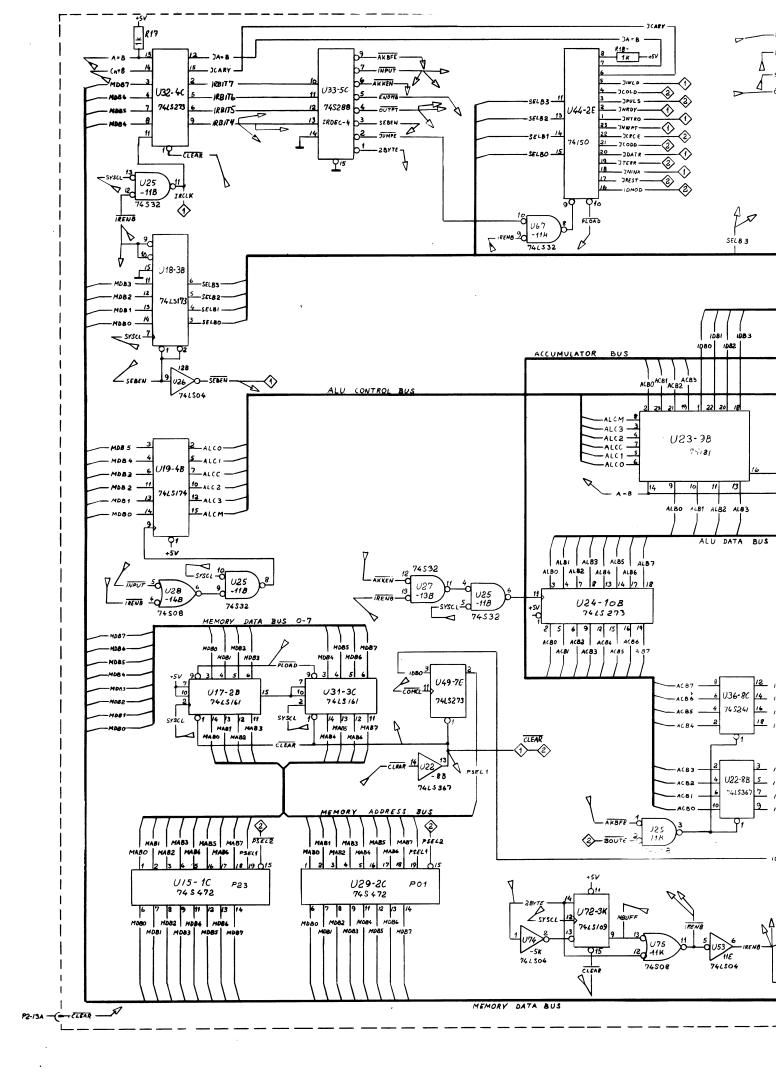

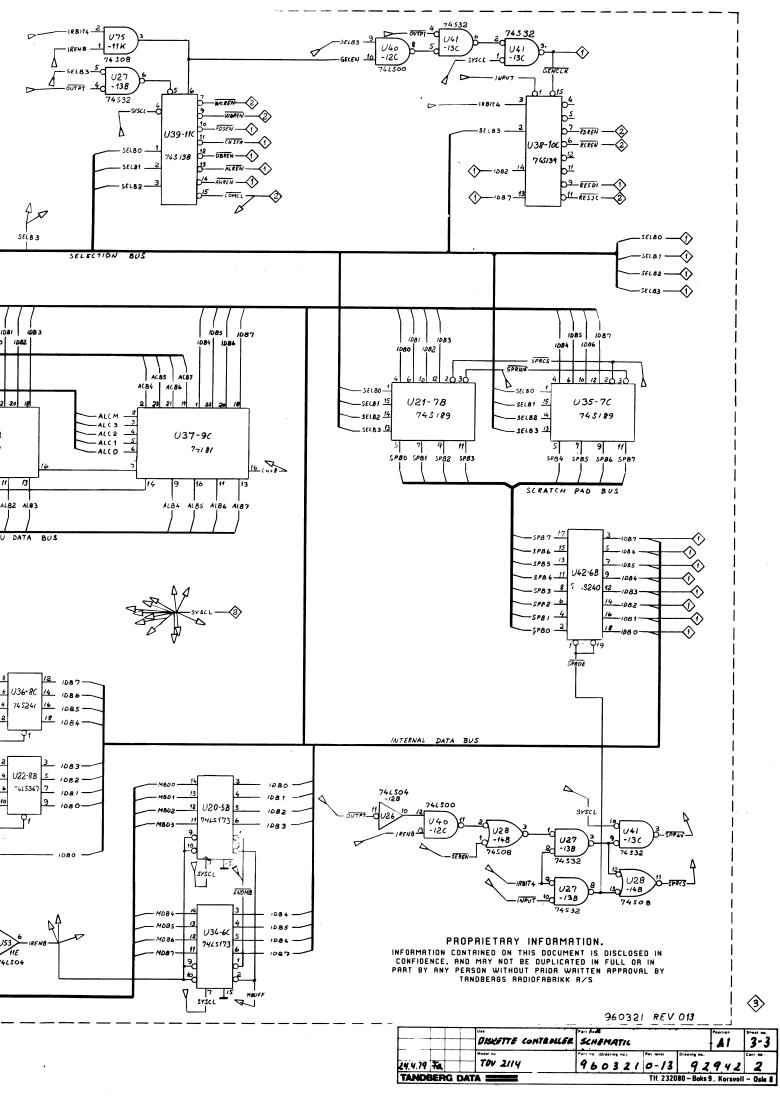

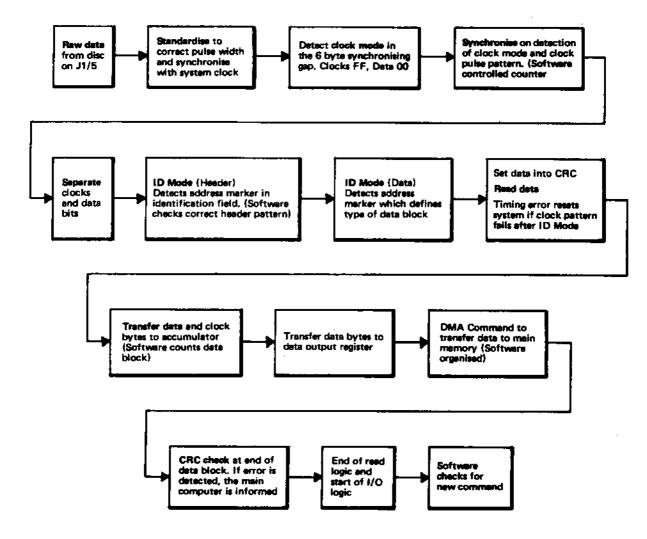

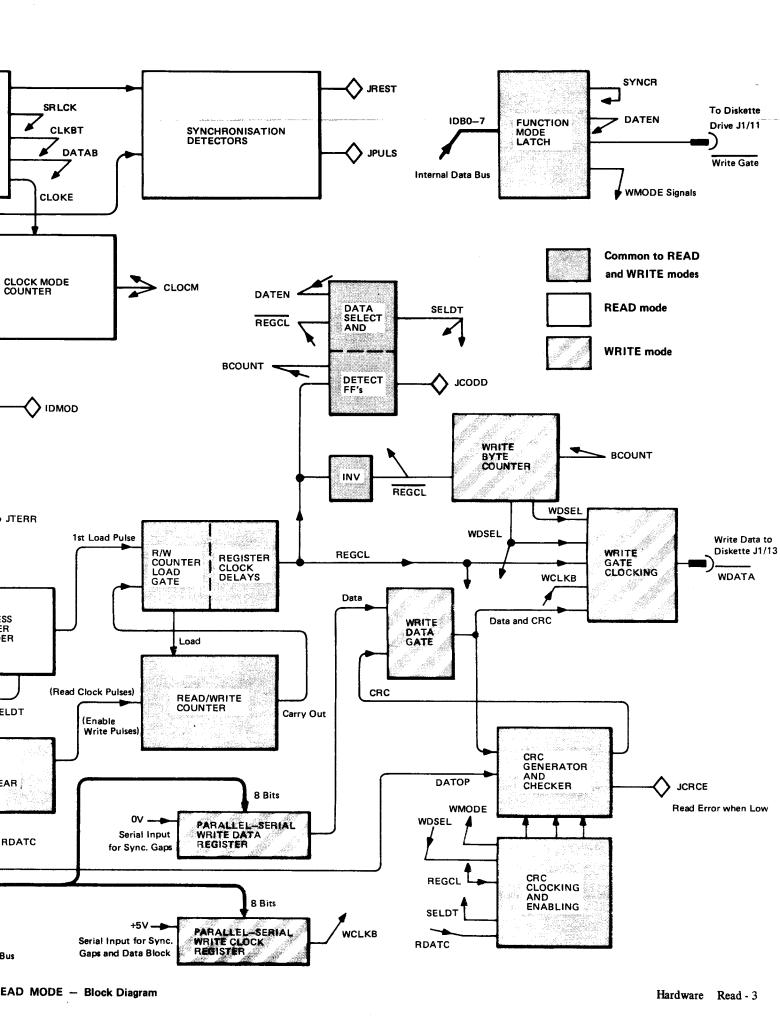

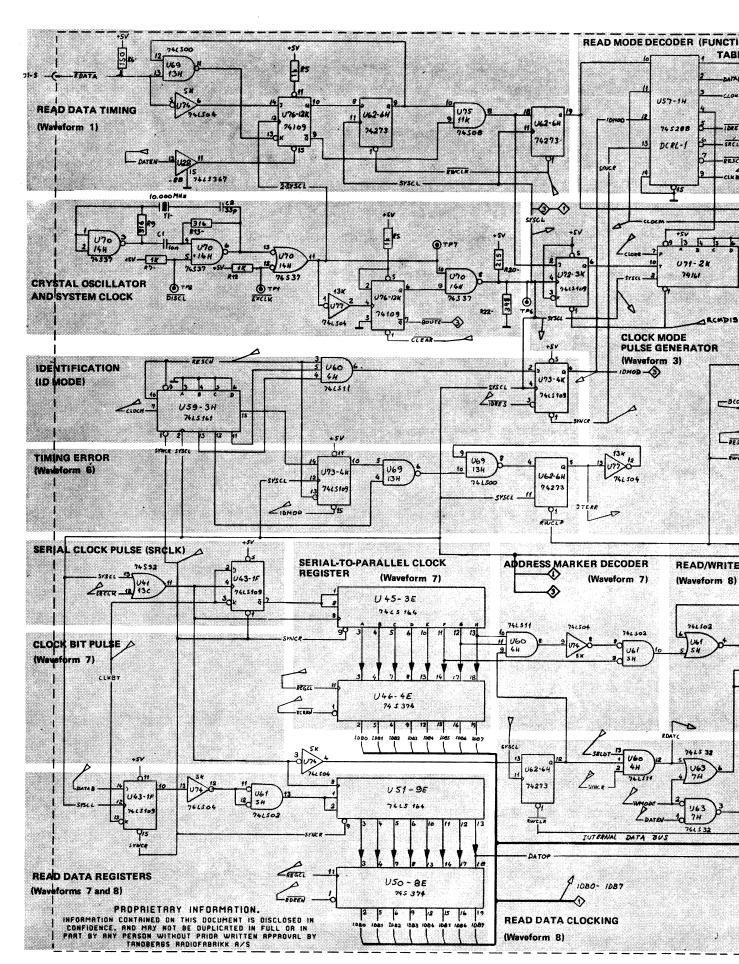

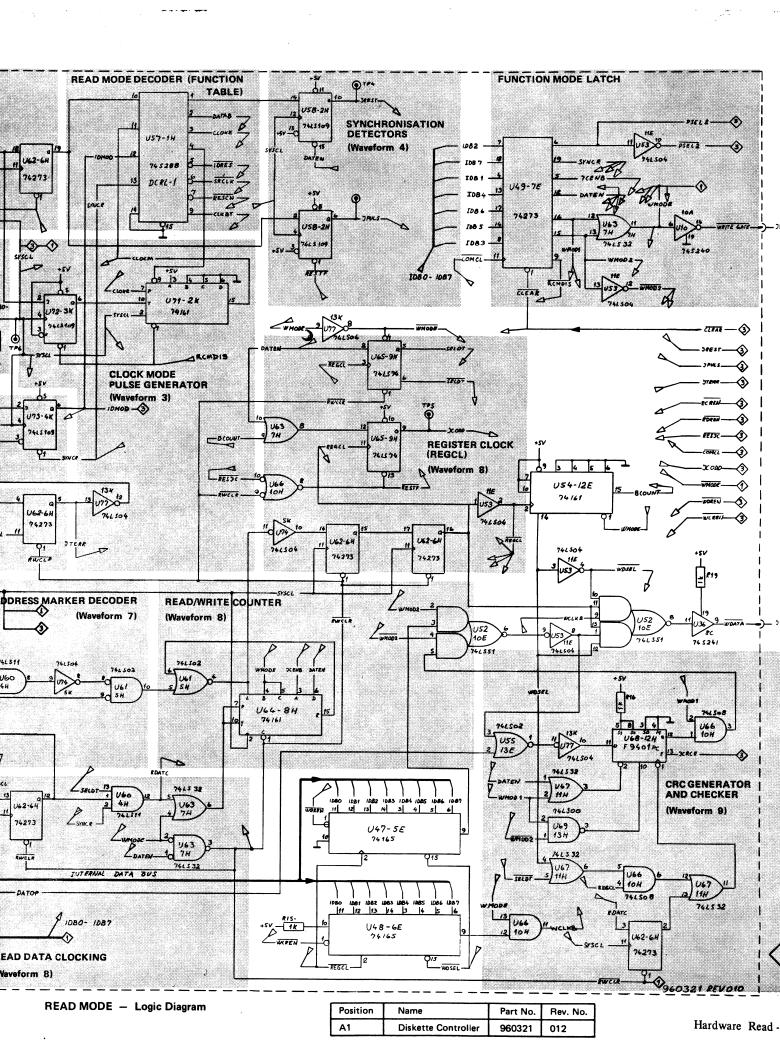

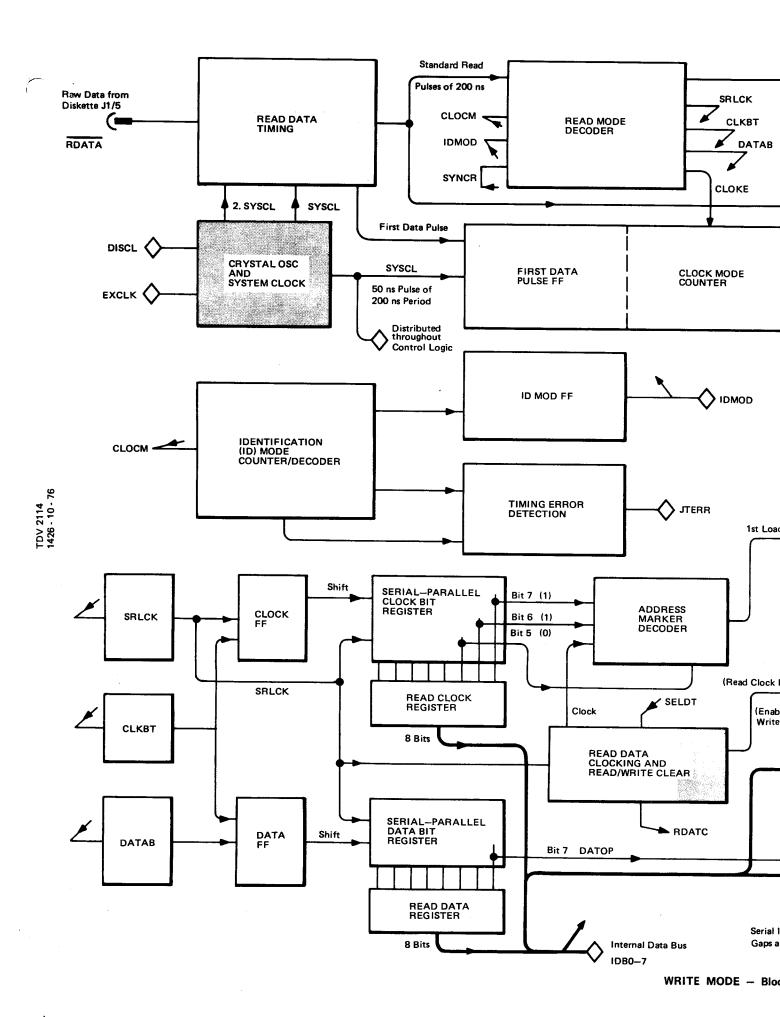

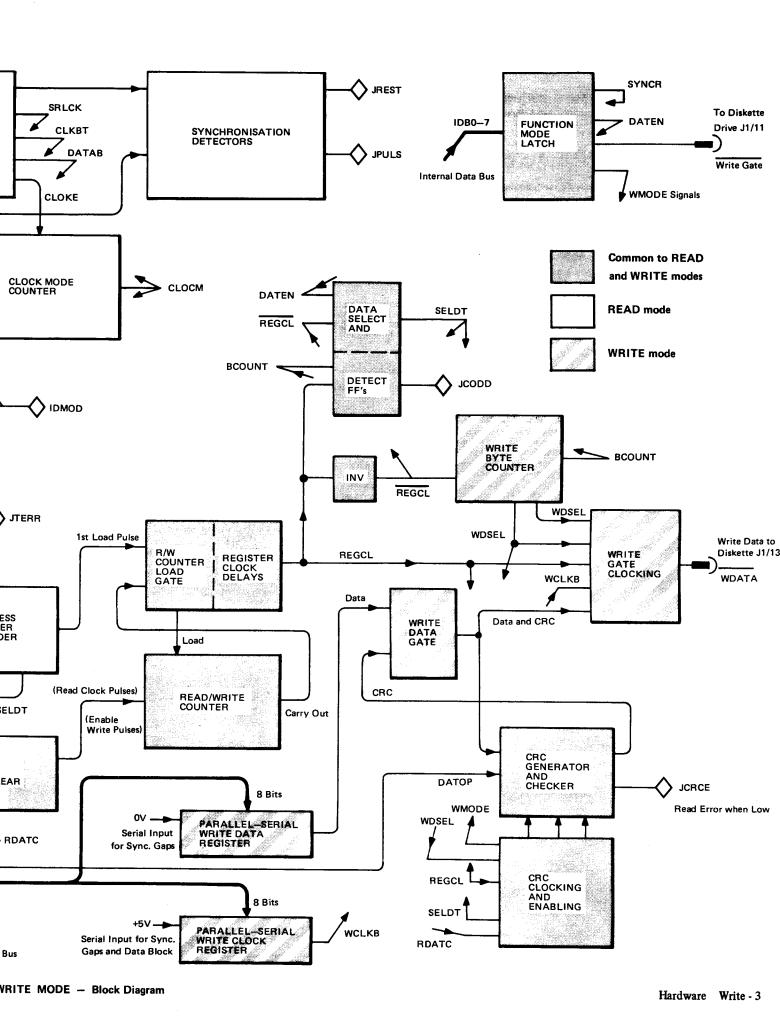

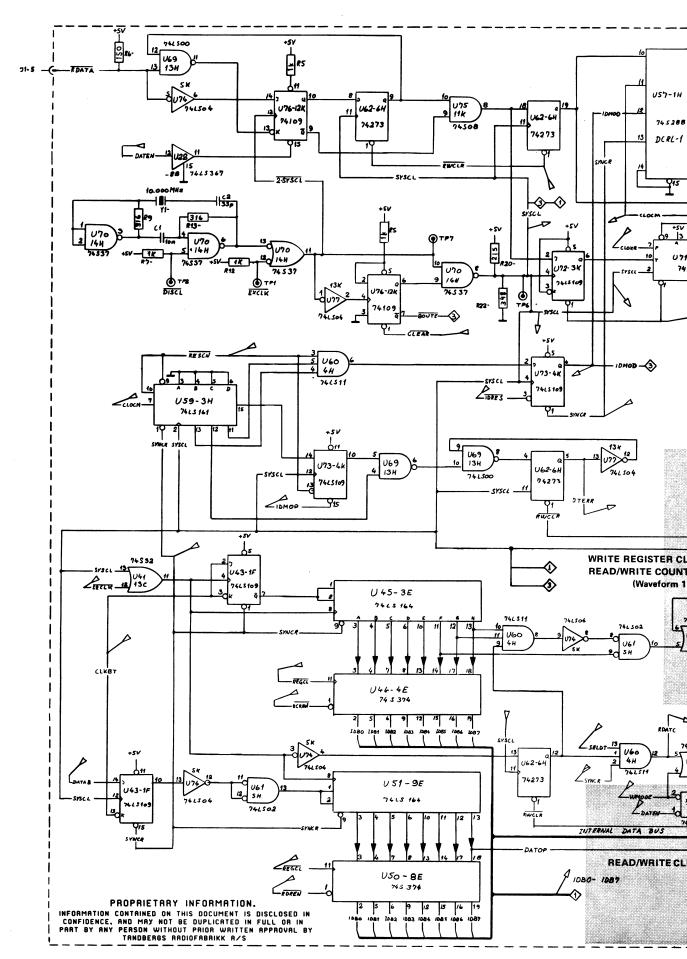

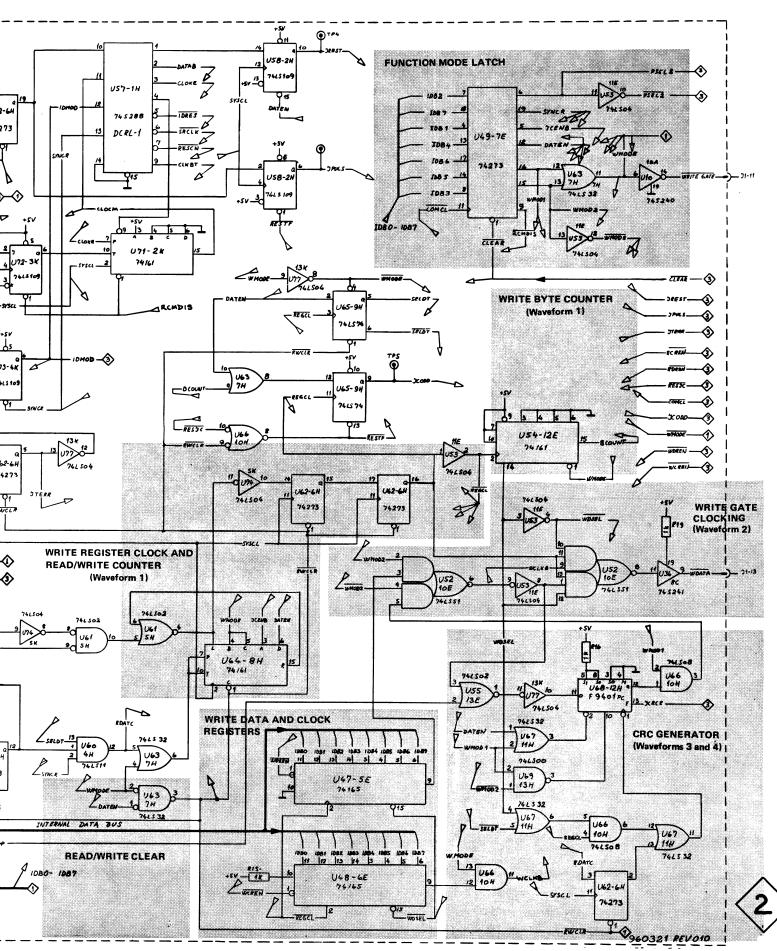

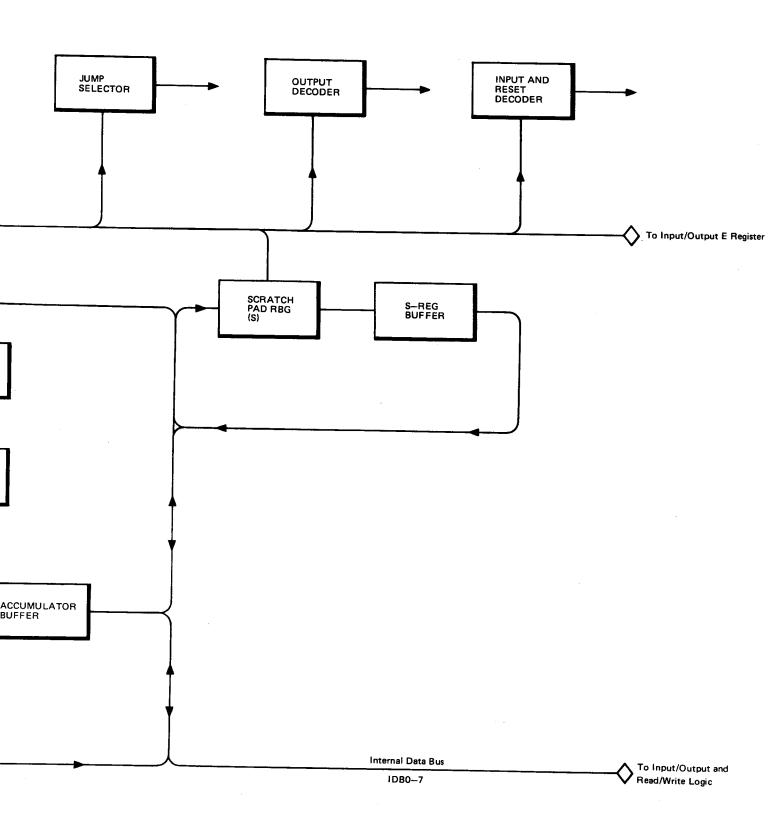

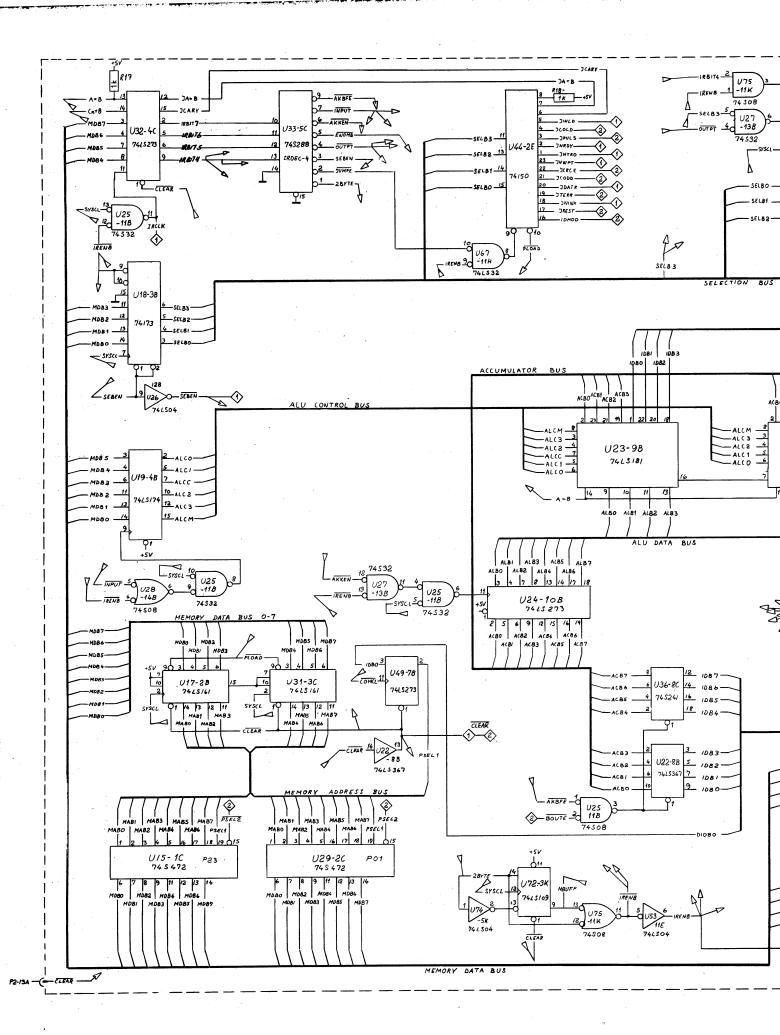

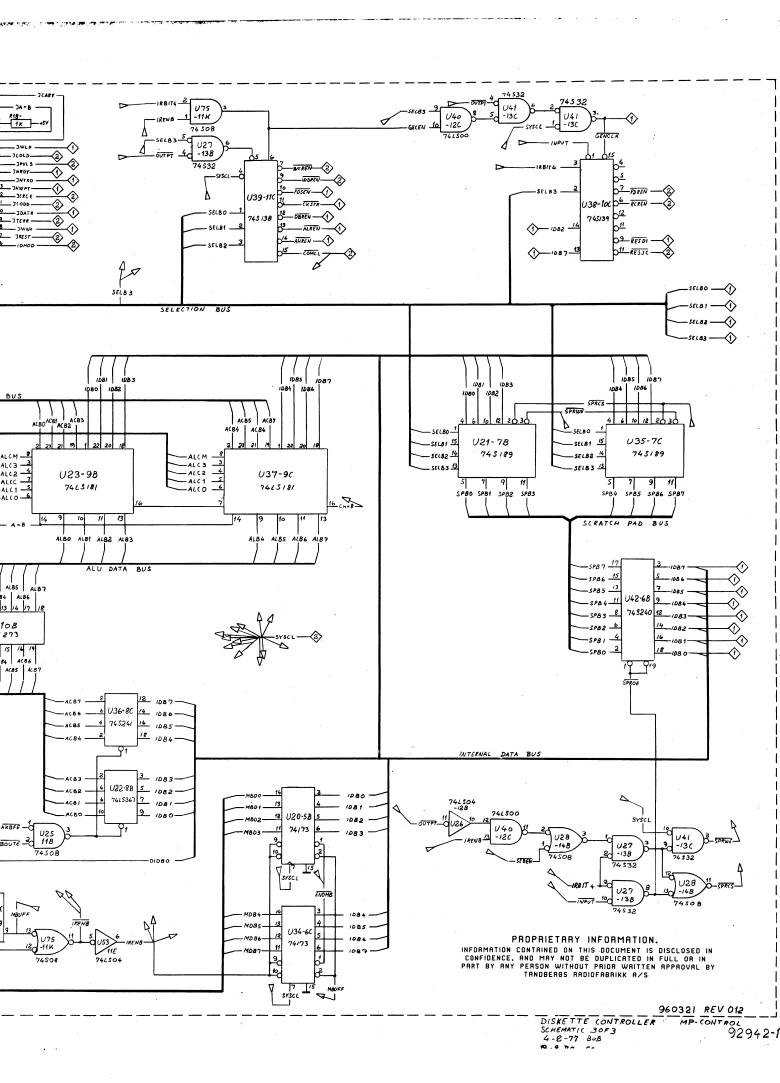

The diskette controller logic is shown in Figure 2, and is divided up into four main functions:-

Input/Output 1)

This logic controls the flow of data between the main computer and the controller and provides the initial indications to the internal processor that the main computer requires attention.

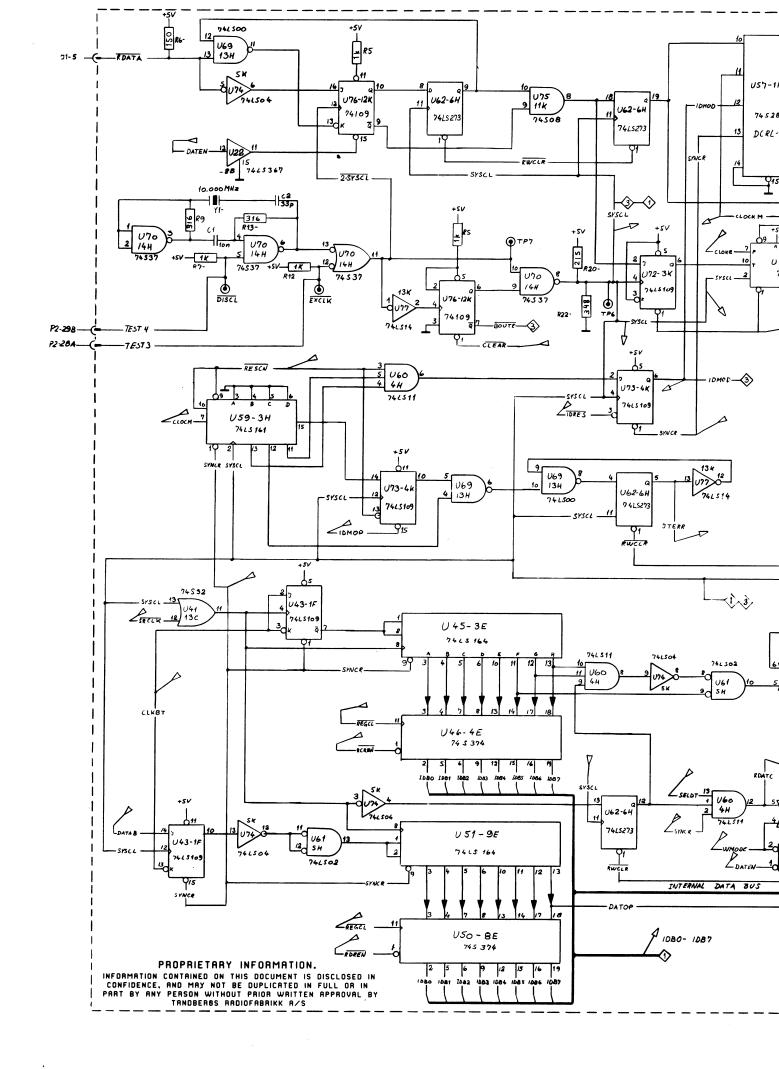

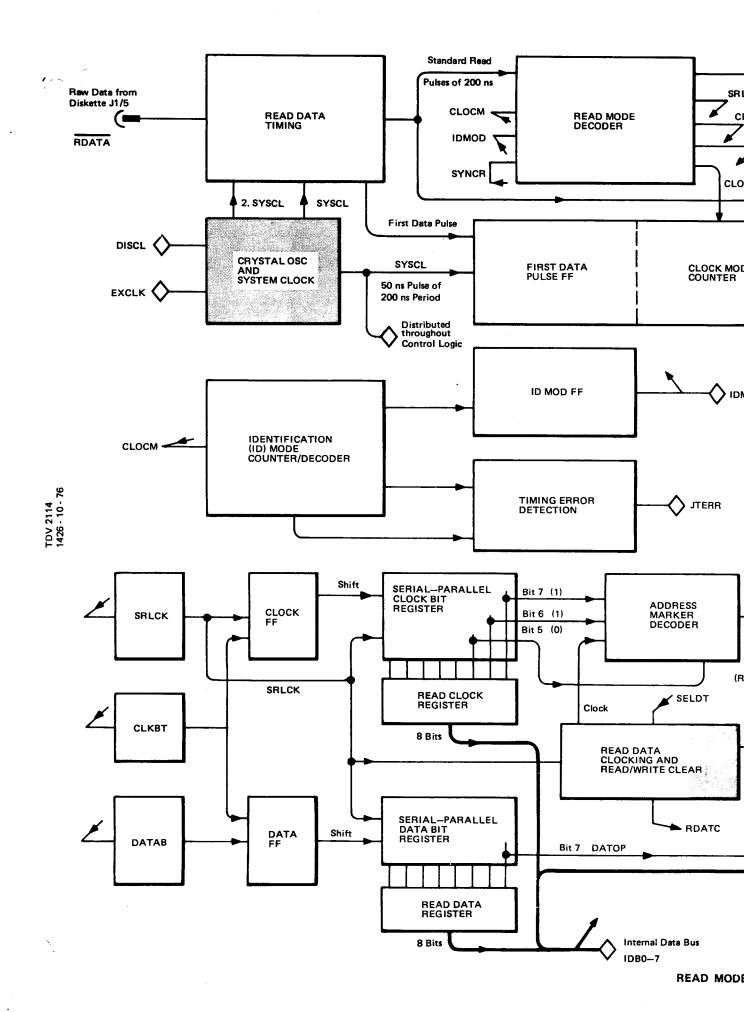

#### 2) Read

This logic receives data from the diskette, synchronises it with the system clock, counts, checks and transfers it byte by byte to the processor.

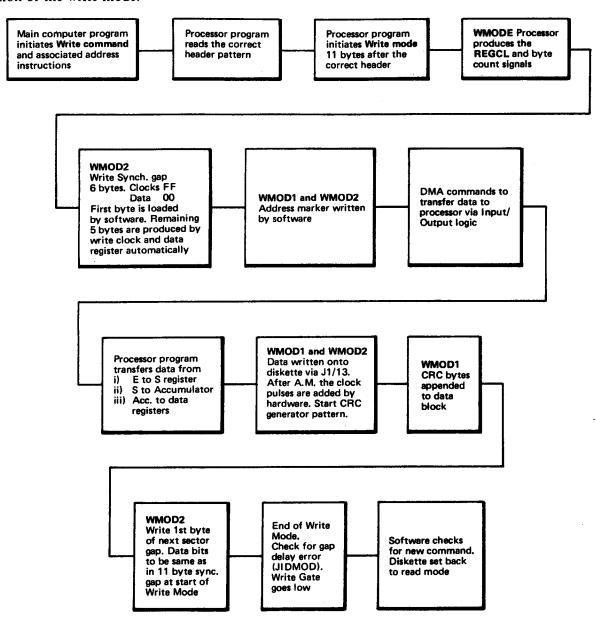

#### 3) Write

This logic receives data from the processor via the input/output logic and writes it byte by byte to the diskette.

#### Processor (internal) 4)

This logic contains the fixed micro-program which controls and co-ordinates the reading and writing of data; initially sets up the diskette and transfers data and status to and from the input/output interface logic.

9

Data is checked after it is read from the diskette to detect whether it is from the correct sector and also to find out if an error has occurred. This checking function is described in the read and write mode logic.

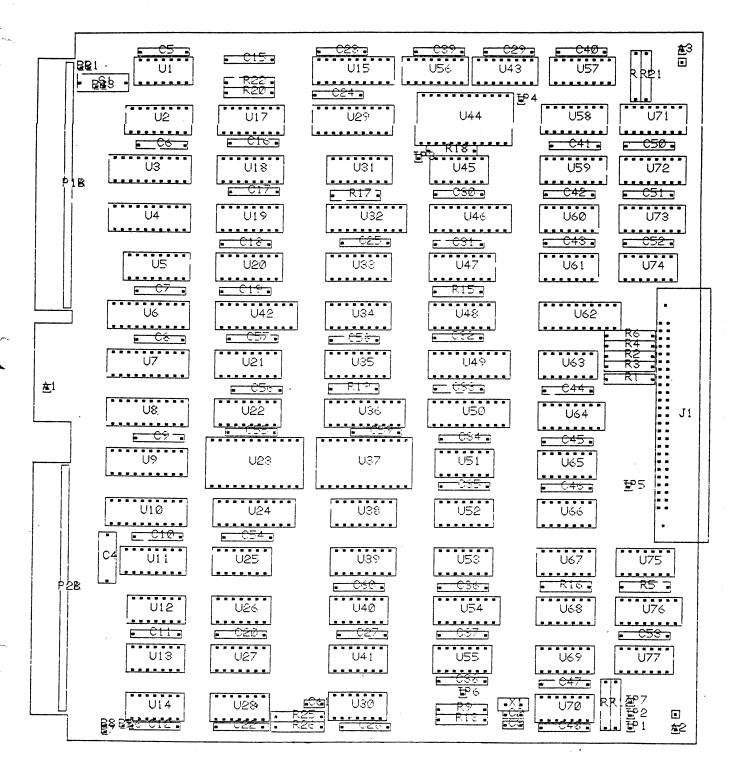

The controller hardware logic is divided into three diagrams, each with an associated functional block diagram. The block diagrams are drawn to correspond with the logic layout to provide easy recognition between the diagram and the description.

Figure 2 Block diagram of Controller

# Recording and Track Format

# Recording Format

The media characteristics, the logical data format, physical data format and the drive characteristics are compatible with the IBM 3740 Data Entry System and 3540 Diskette Input/Output Unit.

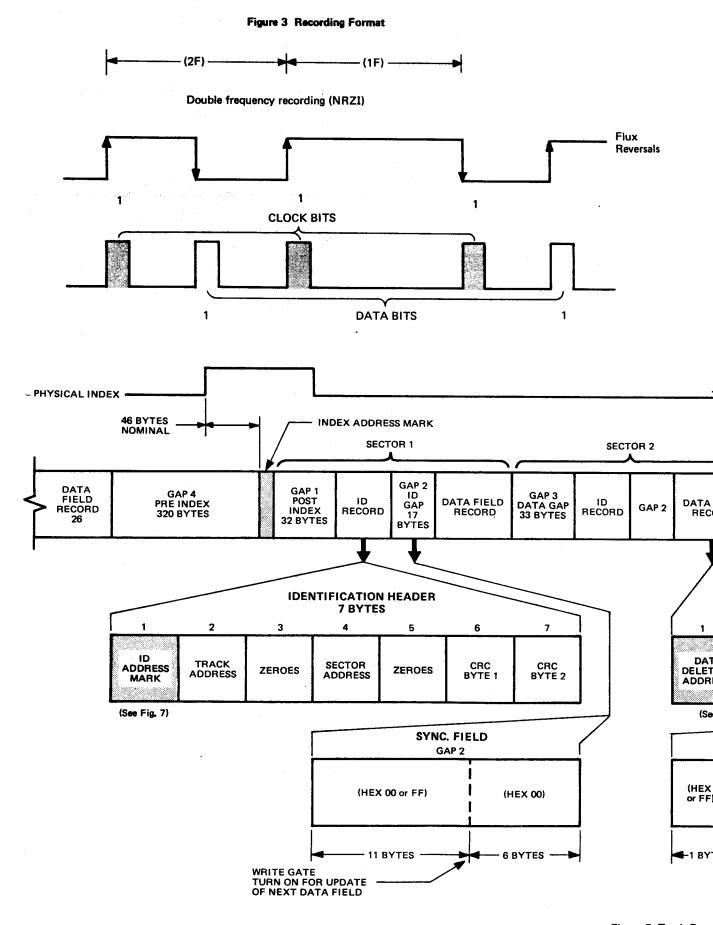

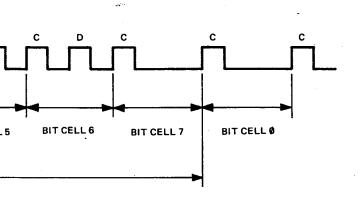

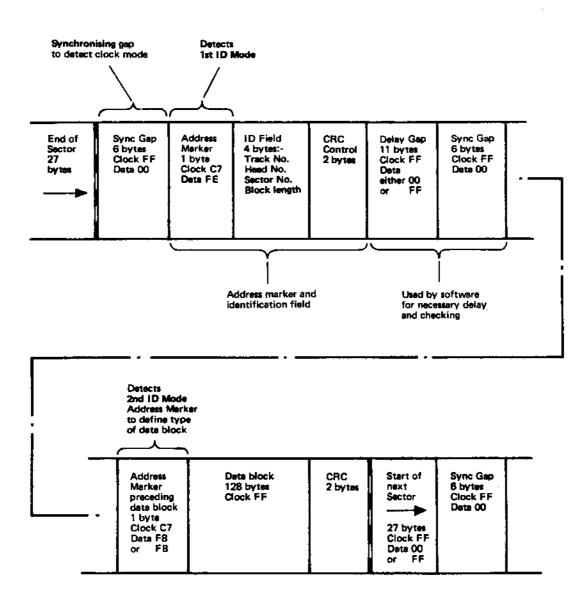

The diskette is initialised by writing each track from beginning to end without interruption. The beginning and end is coincident with the leading edge of the physical index hole. The drive uses the double frequency (2F) horizontal non return to zero (NRZ1) method of recording. Double frequency is the term given to the recording system which inserts a clock bit at the beginning of each bit cell time thereby doubling the frequency of recorded bits. The clock bit, as well as the data bit, are provided by the using system.

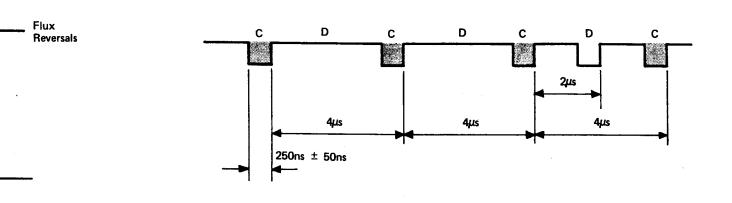

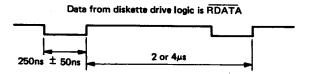

The presence of a flux transition represents a binary one and the absence of a transition represents a binary zero. The development of data bits is shown in Figure 3 and the timing between clock and data pulses is shown in Figure 4.

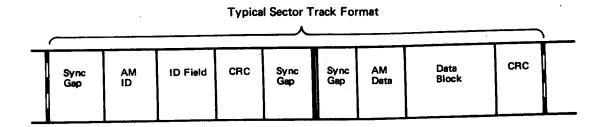

# Track Format

The diskette contains 77 tracks numbered from 00 to 76. The recording density varies from approximately 3200 bits per inch (6400 flux changes per inch) on the inside track to approximately 1700 bits per inch on the outside track.

The logical data format is comprised of an index track format, data track format, alternate and spare track format.

Each diskette is divided into one index track (number 00), 73 data tracks (number 01 to 73), two alternate tracks (numbers 74, 75) and one spare track (number 76).

Each track is divided into 26 sectors. The logical record length of a sector can be anywhere from 1 to 128 characters.

# **Typical Track Index Format**

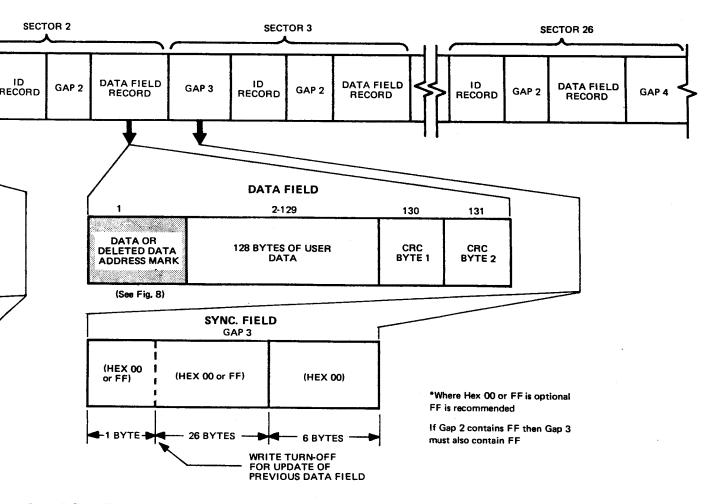

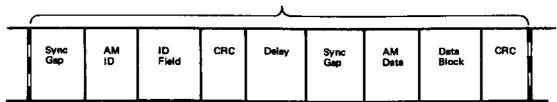

Figure 5 shows a track Format, which is IBM compatible, using Index Recording Format with soft sectoring.

# Soft Sector Recording Format

In this Format, the using system may record one long record or several smaller records. Each track is started by a physical index pulse and then each record is preceded by a unique recorded identifier. This type of recording is called soft sectoring.

# Gaps

Each field on a track is separated from adjacent fields by a number of bytes containing no data bits. These areas are referred to as gaps and are provided to allow the updating of one field without affecting adjacent fields. As can be seen from Figure 5, there are four different types of gaps on each track.

# Gap 1 Post-Index Gap

This gap is defined as the 32 bytes between Index Address Mark and the ID Address Mark for Sector one (excluding the address mark bytes). This gap is always 32 bytes in length and is not affected by any updating process.

# Gap 2 ID Gap

The seventeen bytes between the ID Field and the Data Field is defined as Gap 2 (ID Gap). This gap may vary in size slightly after the Data Field has been updated.

# Gap 3 Data Gap

The thirty-three bytes between the Data Field and the next ID Field is defined as Gap 3 (Data Gap). As with the ID Gap, the Data Gap may vary slightly in length after the adjacent Data Field has been updated.

# Gap 4 Pre-Index Gap

The three hundred and twenty bytes between the last Data Field on a track and the Index Address Mark is defined as Gap 4 (Pre-Index Gap). Initially, this gap is nominally 320 bytes in length; however, due to write frequency tolerances and disk speed tolerances this gap may vary slightly in length. Also, after the data field of record 26 has been updated, this gap may again change slightly in length.

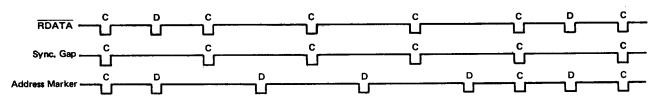

# Address Marks

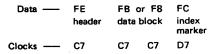

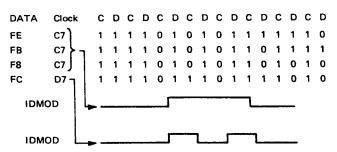

Address Marks are unique bit patterns one byte in length which are used in this typical recording format to identify the beginning of ID and Data Fields and to synchronise the descrialising circuitry with the first byte of each field. Address Mark bytes are unique from all other data bytes in that certain bit cells do not contain a clock bit (all other data bytes have clock bits in every bit cell). There are four different types of Address Marks used. Each of these are used to identify different types of fields.

# Index Address Mark

The Index Address Mark is located at the beginning of each track and is a fixed number of bytes in front of the first record. The bit configuration for the Index Address Mark is Hex. FCD 7.

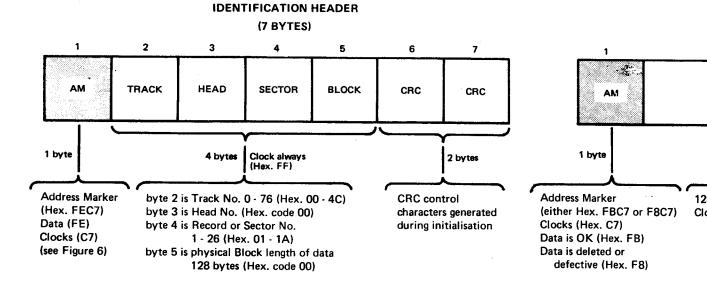

# **ID Address Mark**

The ID Address Mark byte is located at the beginning of each ID Field on the diskette. The bit configuration for this Address Mark is shown in Figure 6 (Hex. FEC7).

# Data Address Mark

The Data Address Mark byte is located at the beginning of each nondeleted Data Field on the diskette. The bit configuration for this Address Mark is Hex. FBC7.

# Deleted Data Address Mark

The Deleted Data Address Mark byte is located at the beginning of each deleted Data Field on the diskette. The bit configuration for this Address Mark is Hex. F8C7.

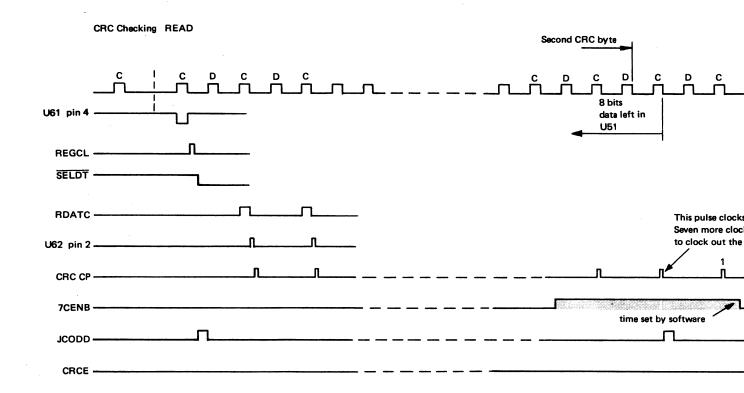

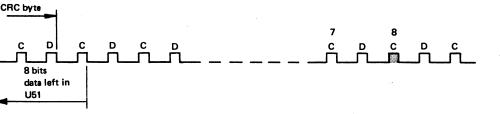

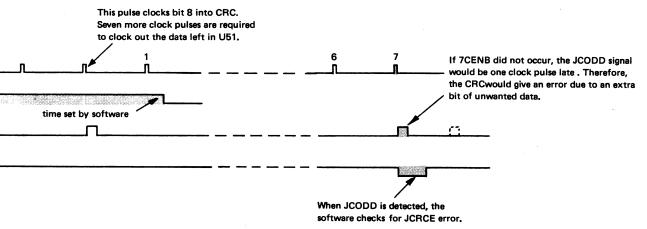

# CRC

Each field written on the diskette is appended with two Cyclic Redundancy Check (CRC) bytes. These two CRC bytes are generated from a cyclic permutation of the data bits starting with bit zero of the address mark and ending with bit seven of the last byte within a field (excluding the CRC bytes). When a field is read back from a diskette, the data bits (from bit zero of the address mark to bit seven of the second CRC byte) are divided by the same generator polynomial. A non-zero remainder indicates an error within the data read back from the drive while a remainder of zero indicates the data has been read back correctly from the diskette.

# Software

The internal processor contains a fixed programmed read only memory which controls all diskette operations. It is accessed automatically after the main computer program requests attention.

Certain decoding functions are electrically preprogrammed, therefore, it is essential that all software and decoder tables are available for the complete understanding of the controller hardware actions.

The following software information is contained in the software section of this manual.

- 1) Input/Output Instructions and commands

- 2) Controller micro-program instructions

- 3) Controller program flow charts

- 4) Controller program codes.

Figure 5 Track Form

Figure 4 Clock and Data Timing

Figure 5 Track Format

С

BIT CELL 7

BIT CELL Ø

BIT CELL 1

BIT CELL 3 BIT CELL 5 BIT

Figure 6 ID Address Mark

ID ADDRESS MARK BYTE -

# DATA BITS CLOCK BITS DATA BITS CLOCK BITS DATA BITS CLOCK BITS CLOCK BITS CLOCK BITS DATA BITS CLOCK BITS

BIT CELL 2

Figure 7

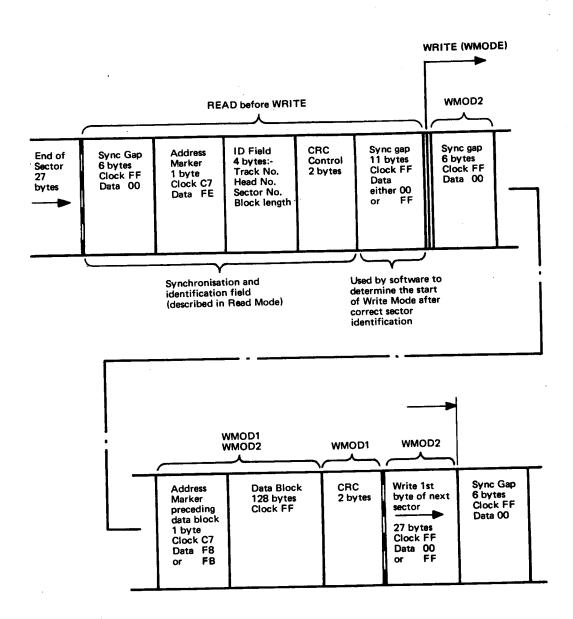

# **DATA FIELD** (131 BYTES) 2 - 129 130 131 DATA CRC CRC 2 bytes 128 bytes of data **CRC** control F8C7) Clocks always (Hex. FF) characters generated during the write operation

Figure 8

# **Signal Definitions**

A mnemonic is an abbreviation for the signal name, for example DATEN = Data Enable.

The signal name states the purpose or function of the signal.

The signal is said to be true or false depending on whether the statement in the signal name is true or false.

When the signal is **true** its logic value is 1. When the signal is **false** its logic value is 0.

A bar above the mnemonic (e.g. BOUTE) means an inversion of the logic value.

Example:

|              | Logic Value |       |  |

|--------------|-------------|-------|--|

| Signal state | BOUTE       | BOUTE |  |

| True         | 1           | 0     |  |

| False        | 0           | 1     |  |

Inside the controller the logic signal levels are

0 to + 0.7 volts + 2.5 to 5 volts Logic 0 Logic 1

# **Other Connection Details**

To avoid the circuit diagram being crowded with lines, many interconnections are merely indicated by the signal mnemonic and an arrow.

Example: DATEN To enother place on the same diagram.

DATEN From another place on the same diagram.

To or from another place on another diagram, but on the same board.

| Mnemonic          | Signal name                                       | Source                                           | Destination/s                                                                   | Effect of signal                                                                                                                                                                                                                         |  |

|-------------------|---------------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ABS. M.B.         | Absolute most sign, bit                           | Registers                                        | _                                                                               | Indicates most signification bit position                                                                                                                                                                                                |  |

| A = B1            | Input B1 (bit 0 - 3) is equal with A1 (bit 0 - 3) | ALU register<br>U23 pin 14                       | U32 pin 13                                                                      | Produces jump instruction JA = B                                                                                                                                                                                                         |  |

| A = B2            | Input B2 (bit 4 - 7) is equal with A2 (bit 4 - 7) | ALU register<br>U37 pin 14                       | U32 pin 13                                                                      | Compares Acc, bits with internal data bus<br>Produces jump instruction JA = B                                                                                                                                                            |  |

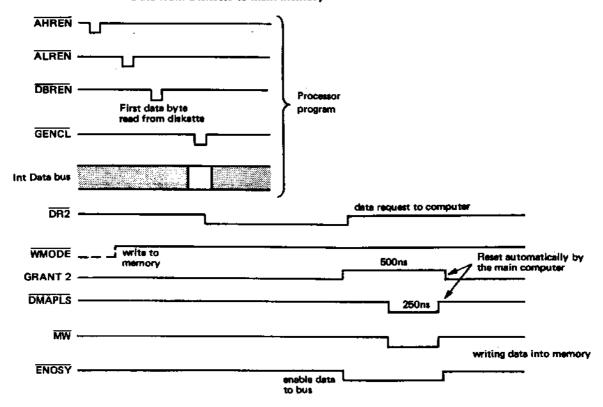

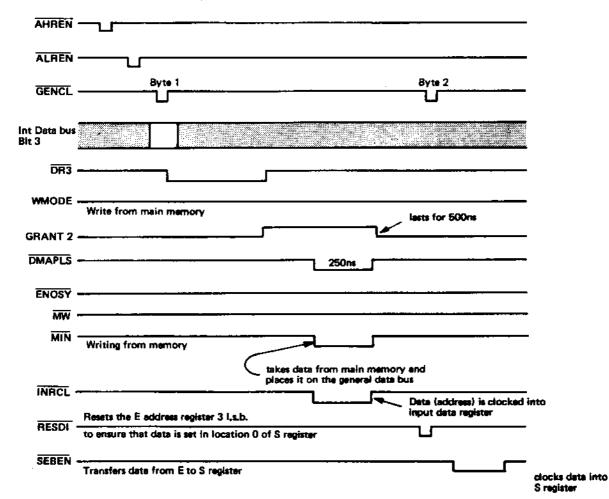

| AHREN             | Address high register enable                      | Output decoder<br>U39 pin 14                     | U3 pin 11                                                                       | Clocks in address to high reg. from internal data bus for DMA transfers                                                                                                                                                                  |  |

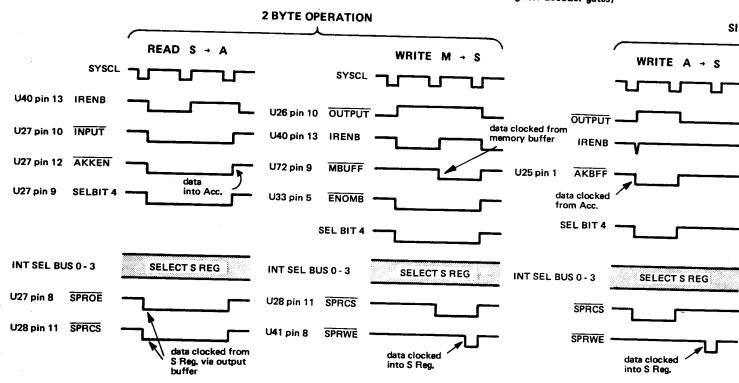

| AKBFE             | Accumulator buffer enable                         | Inst. decoder<br>U33 pin 9                       | U25 pin 1                                                                       | Enable Acc. buffer                                                                                                                                                                                                                       |  |

| AKKEN             | Accumulator enable                                | Inst. decoder<br>U33 pin 6                       | U27 pin 12                                                                      | Enables Acc.                                                                                                                                                                                                                             |  |

| ALREN             | Address low register enable                       | Output decoder<br>U39 pin 13                     | U4 pin 11                                                                       | Clocks in address to low reg. from internal data bus for DMA transfers                                                                                                                                                                   |  |

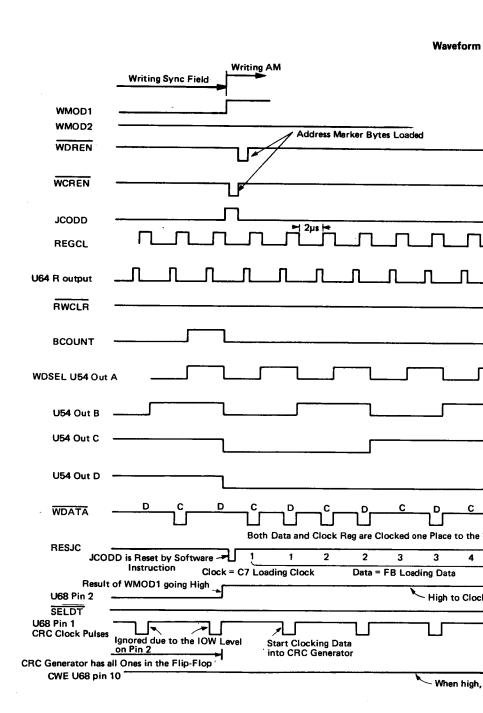

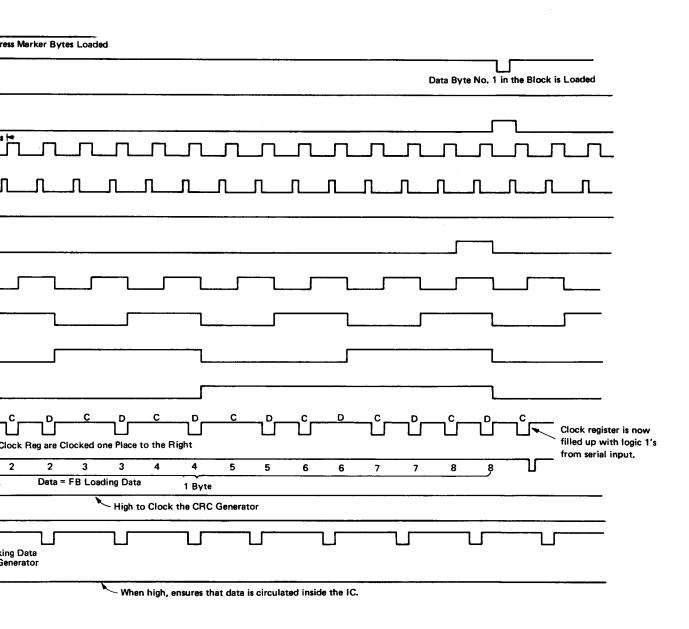

| BCOUNT            | Block count                                       | Write byte counter<br>U54 pin 15                 | U63 pin 9                                                                       | Enables JCODD after every byte. counted up by 16 REGCL pulses                                                                                                                                                                            |  |

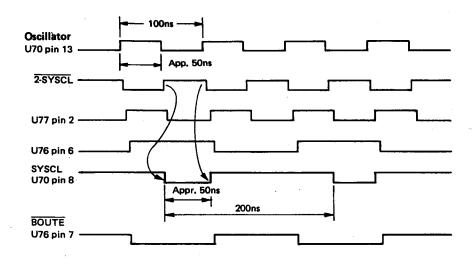

| BOUTE             | Buffer output enable                              | Oscillator<br>U76 pin 7                          | U25 pin 2                                                                       | To ensure that the logic enables Acc. buffer in phase with system clock and also provide 1:1 pulse width to give the Acc. buffer sufficient time to place its contents on the dobus. The Acc. buffer is enabled slightly ahead of SYSCL. |  |

| CDATA             | Clock data                                        | Write clock reg.<br>U66 pin 11                   | U52 pin 9                                                                       | Writes clock bits from write clock register to disk at 4µs intervals                                                                                                                                                                     |  |

| CLEAR             | Clear                                             | Interface signal<br>(P2 - A13)<br>U22 pin 14     | Bistables and counters                                                          | After 500ms without new command it resets 0 on processor interface and r/w logic. Unloa heads but does not return to track 0. Does not stop 2 x SYSCL so that a full SYSCL pulse c start at the correct time after CLEAR has go          |  |

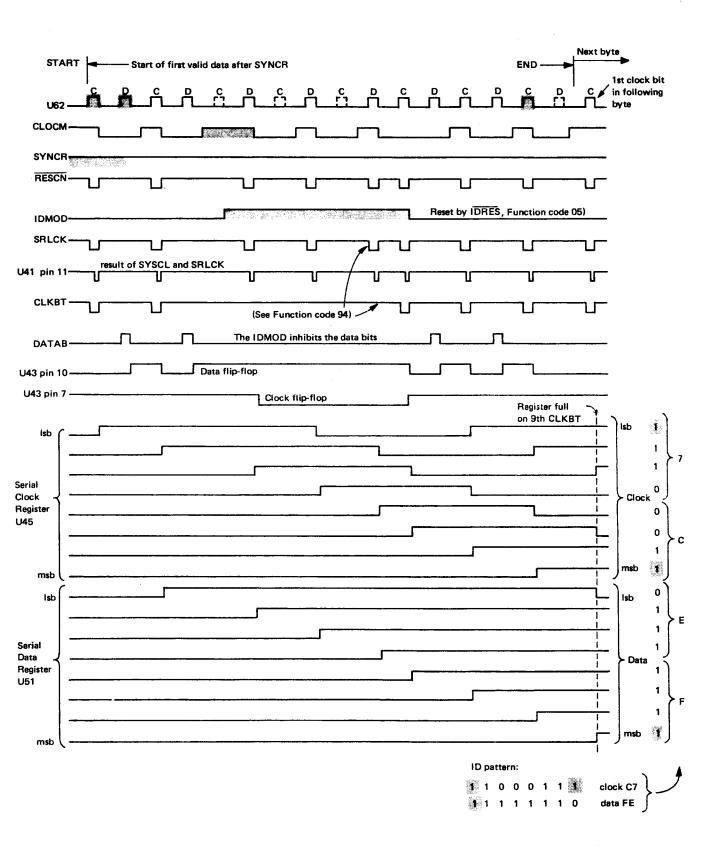

| CLKBT             | Clock bit                                         | Read decoder<br>U57 pin 9                        | U43 pins 2,3                                                                    | When in either CLOCM or ID MODE producting input to read clock bistable when detecting clock pulses                                                                                                                                      |  |

|                   |                                                   |                                                  | U43 pin 13                                                                      | Enables K input on read data bistable when detecting data pulses                                                                                                                                                                         |  |

| CKSTR             | Clock status register                             | Output decoder<br>U39 pin 11                     | U7 pin 11                                                                       | Clocks in data to status reg. from Acc. and Mem. buffer                                                                                                                                                                                  |  |

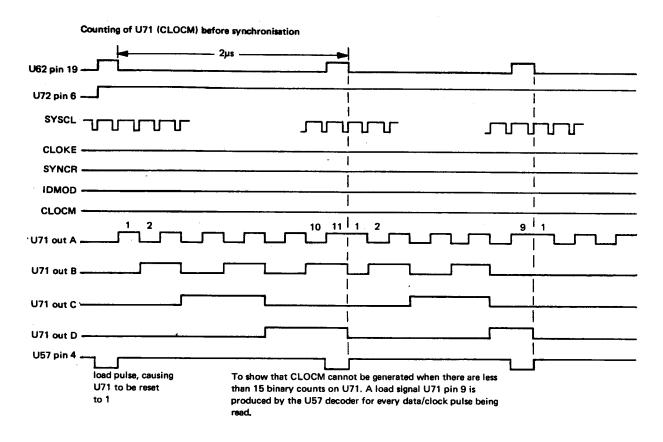

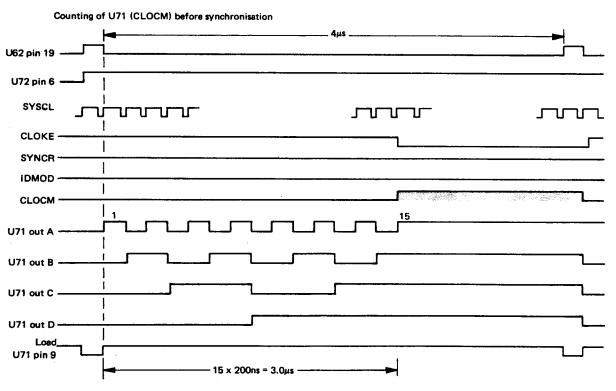

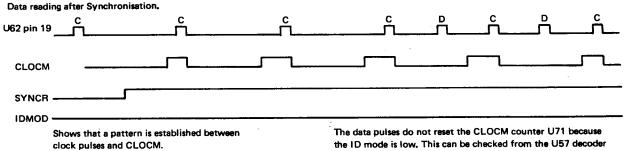

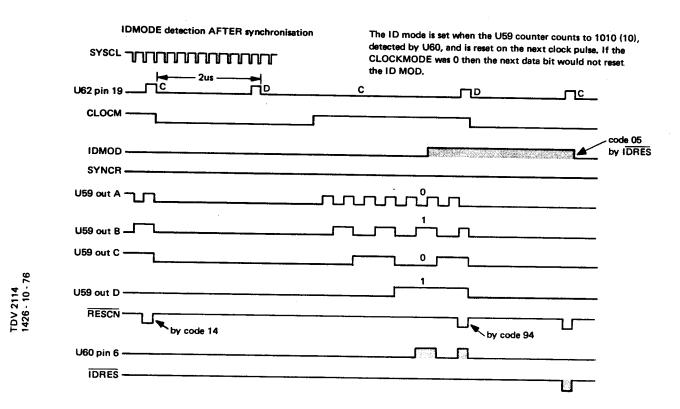

| CLOCM Clock mode  | Syncr. counter<br>U71 pin 15                      | U57 pin 11                                       | Read decoder input, Occurs after 15 SYSCL pulses when RDATA is at 4µs intervals |                                                                                                                                                                                                                                          |  |

|                   |                                                   |                                                  | U59 pin 7                                                                       | Enables ID counter to count to 110 and indicates the ID MODE.                                                                                                                                                                            |  |

| CLOKE             | Clock enable                                      | Read decoder<br>U57 pin 3                        | U71 pin 7                                                                       | Enables syncr, counter but inhibits when no<br>read pulse occurs. Maintains CLOCM during<br>ID pattern                                                                                                                                   |  |

| C <sub>n</sub> +8 | Carry output from ALU                             | ALU register<br>U37 pin 16                       | U32 pin 14                                                                      | Produce jump instruction JCARY when a<br>carry out signal from combined ALU registe<br>is indicated                                                                                                                                      |  |

| COMCL             | Combined clock                                    | Output decoder<br>U39 pin 15                     | U49 pin 11                                                                      | Enable mode decoder, Selects from internal DB0 - 7                                                                                                                                                                                       |  |

|                   | ····                                              |                                                  | U49 pin 9                                                                       | (see also memory counter extension)                                                                                                                                                                                                      |  |

| COMOR             | Command or data registered                        | General address bus<br>decode logic<br>U61 pin 1 | U2 pin 3                                                                        | Sets bistable in input add. reg. to produce<br>JCOLD when command instruction occurs                                                                                                                                                     |  |

| DATAB             | Data bit                                          | Read decoder<br>U57 pin 2                        | U43 pin 14                                                                      | Data pulse to set serial read input bistable                                                                                                                                                                                             |  |

| DATEN             | Data enable                                       | Mode decoder<br>U49 pin 12                       | U58 pin 15                                                                      | Resets SYNC STATUS bistable until CLOCH is established                                                                                                                                                                                   |  |

|                   |                                                   |                                                  | U63 pin 1                                                                       | Clears write/read counter at the start of read mode prior to SYNCR.                                                                                                                                                                      |  |

|                   |                                                   |                                                  | U63 pin 10                                                                      | Sets JCODD at end of each data byte when<br>w/r counter produces REGCL                                                                                                                                                                   |  |

|                   |                                                   |                                                  | U65 pin 2                                                                       | Sets SELDT upon detection of A.M. when clock decoder circuit produces REGCL                                                                                                                                                              |  |

|                   |                                                   |                                                  | U67 pin 1                                                                       | Presets CRC generator before SYNCR occurs                                                                                                                                                                                                |  |

|                   |                                                   |                                                  | U64 pin 6                                                                       | Presets write/read counter to 8 after SYNCR for bit-counting to 15                                                                                                                                                                       |  |

|                   |                                                   |                                                  | U22 pin 12                                                                      | Resets read data and SYSCL timing logic untitle CLOCK MODE is established, at the star syncr. MODE.                                                                                                                                      |  |

| DATOP             | Data operation                                    | Read ser/par reg.<br>U51 pin 13                  | U55 pin 2                                                                       | Serial data stream, monitored by CRC during<br>read operation                                                                                                                                                                            |  |

| BREN              | Data bus register enable                          | Output decoder<br>U32 pin 12                     | U6 pin 11                                                                       | Clocks in from DB internal                                                                                                                                                                                                               |  |

| Mnemonics | Signal name                 | Source                           | Destination/s                                                    | Effect of signal                                                                                                                                                                                             |                                          |

|-----------|-----------------------------|----------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| DISCL     | Disable clock (external)    | TP2                              | Oscillator<br>U70 pin 5                                          | External signal applied to the test point to inhibit the oscillator                                                                                                                                          |                                          |

| DMAPLS    | DMA pulse                   | Interface signal<br>P2 A20       | U55 pin 6                                                        | With GRANT, enables the data transfer to or from main memory to proceed                                                                                                                                      |                                          |

| DR2       | DMA request No. 2           | Interface signal<br>U13 pin 6    | P1 A21                                                           | Informs computer that disk is ready to accept data transfer when in the DMA mode. Computer sends GRANT                                                                                                       |                                          |

| ENOMB     | Enable output memory buffer | Inst. decoder<br>U33 pin 5       | U20 pin 1<br>U34 pin 1                                           | Enables the memory buffer register contents<br>to be placed on the internal data bus — but<br>not during a 2-byte operation because of<br>MBUFF                                                              |                                          |

| ENOSY     | Enable output system        | Interface logic<br>U14 pin 11    | U6 pin 1                                                         | Enables the output data register when writing to main memory during a DMA transfer                                                                                                                           |                                          |

| EXCLK     | External clock              | TP1                              | Oscillator<br>U70 pin 12                                         | External clock to replace oscillator for test purposes                                                                                                                                                       |                                          |

| FDSEN     | Floppy disk system enable   | Output decoder<br>U39 pin 10     | U9 pin 11                                                        | Clocks the floppy disk register for disk selection, direction and track position pulses                                                                                                                      |                                          |

| GECEN     | General clock enable        | Output decoder<br>U75 pin 3      | U40 pin 10                                                       | Anded with bit 3 to produce GENCL for an m.p. data/device transfer. Inhibited during a 2 byte operation because of IRENB                                                                                     |                                          |

| GENCL     | General clock               | Output decoder<br>U41 pin 3      | U38 pin 15                                                       | Clocks R1/R2 register for a DMA data transfer instruction                                                                                                                                                    |                                          |

|           |                             | ·                                | U13 pin 11<br>U13 pin 3                                          | Clocks interrupt register for status transfer instruction (Controlled I/O). With bit 3 sets up data request for DMA transfers. Response from computer is GRANT                                               |                                          |

| GRANT 2   | Grant No. 2                 | Interface signal<br>P1 B11       | U26 pin 1<br>U14 pin 13                                          | The computer acknowledgement to a DMA data request by No. 2. Priority . Enables DMA logic                                                                                                                    |                                          |

| GRANT 2   | rant No. 2                  |                                  | Interface logic<br>U26 pin 2                                     | U55 pin 5                                                                                                                                                                                                    | Anded with DMAPLS to allow a DMA transfe |

|           | 026 pm 2                    | U11 pin 15                       | Enables acknowledge signal to computer to<br>send or accept data |                                                                                                                                                                                                              |                                          |

|           |                             |                                  | U12 pin 4                                                        | Resets data request bistable each time a reque is made                                                                                                                                                       |                                          |

|           |                             |                                  | U3 pin 1<br>U4 pin 1                                             | Enables the AHREN and ALREN to be gated<br>to the main computer memory as a 16 bit<br>word                                                                                                                   |                                          |

| IACK 6    | Interrupt acknowledge No.6  | Interface signal<br>P1 A27       | U12 pin 9                                                        | The computer acknowledgement to an interrupt request by interrupt level 6 to transfer status (controlled I/O). Resets interrupt register                                                                     |                                          |

| IDMOD     | Identification mode         | Format decoder<br>U73 pin 6      | U57 pin 12                                                       | (READ mode) Input signal to the Syncr.<br>decoder when the format ID marker is detected                                                                                                                      |                                          |

| ,<br>!    |                             |                                  | U73 pin 15                                                       | Resets JTERR detection bistable after timing error                                                                                                                                                           |                                          |

|           |                             |                                  | U44 pin 16                                                       | Produces jump instruction to indicate error if ID MOD remains in Syncr, gap between read before write mode                                                                                                   |                                          |

| IDRES     | Identification mode reset   | Read decoder<br>U57 pin 5        | U73 pin 3                                                        | Resets ID MOD bistable on the first clock pulse after the missing clocks                                                                                                                                     |                                          |

| INDEX     | Index pulse (see JINDX)     | Disk Interface<br>JF 31          | U56 pin 6                                                        | Indicates start of track, once per revolution of disk. Causes jump instruction. Start point for initialisation                                                                                               |                                          |

| INPUT     | Input                       | Instruction decoder<br>U33 pin 7 | U38 pin 1<br>U27 pin 10<br>U40 pin 2                             | Produces read data and read clock register enabling signals with SEL bit 4, produces S register output enable signals (S → A) clock MD register to ALU for the 2 byte instruction (since IRENB is inhibited) |                                          |

| INCRL     | Input register clock        | Interface logic<br>U12 pin 3     | U2 pin 9                                                         | Clocks input addresses AB0 - AB2 into E register from computer                                                                                                                                               |                                          |

|           |                             |                                  | U8 pin 11                                                        | Clocks input data DB0 - DB7 into E register from computer                                                                                                                                                    |                                          |

| IOIN      | I/O in                      | Interface signal<br>P2A17        | U26 pin 13                                                       | Signal from computer to enable status transfer (controlled) from status register                                                                                                                             |                                          |

| IOW       | I/O write                   | Interface signal<br>P2A19        | U1 pin 3                                                         | Signal from computer to enable the clocking of the input address and data registers. (Controlled transfers)                                                                                                  |                                          |

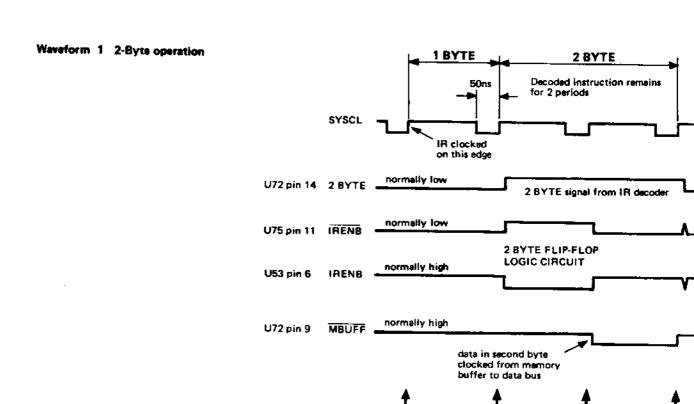

| IRCLK     | Instruction register clock  | IR enable logic<br>U25 pin 11    | U32 pin 11                                                       | Clocks 8 bistables in total:- Outputs 2, 5, 6, 9 to Inst. decoder Outputs 12, 15, 16, 19 to Jump selector Clocks on every SYSCL except in middle of 2 byte operation                                         |                                          |

| Esines, Cel     | Sienel erma                         | Source                                 | Destination/s                                                | Effect of signal                                                                                                                                                                                                                           |

|-----------------|-------------------------------------|----------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

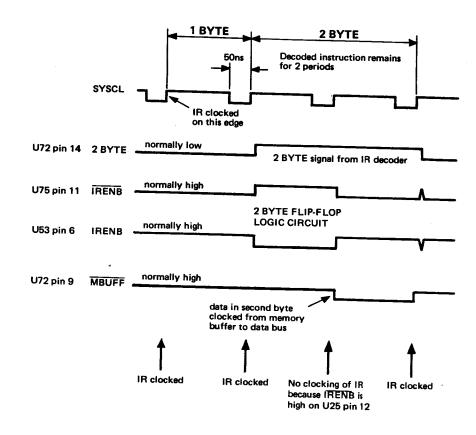

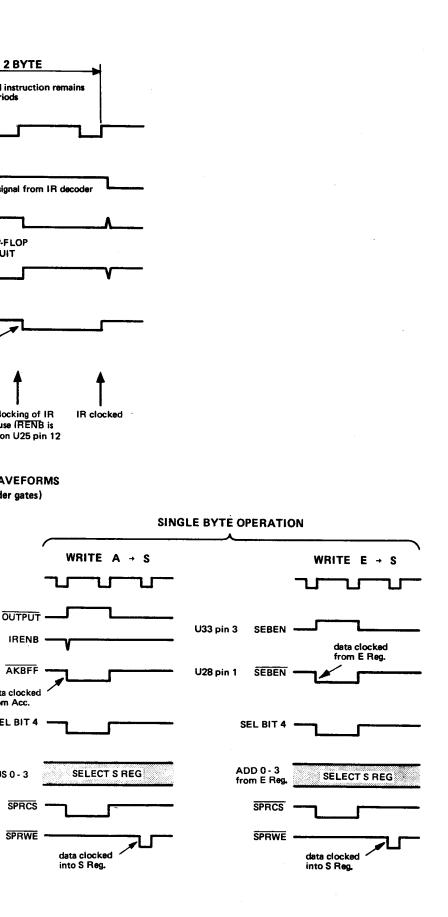

| ច់រ <b>ប់NB</b> | Instruction register enable         | 2 byte logic<br>U75 pin 11             | Normally low,<br>except in 2 byte<br>operation<br>U25 pin 12 | With SYSCL, produces IRCLK enables IR register                                                                                                                                                                                             |

|                 |                                     |                                        | U18 pins 9, 10                                               | With SYSCL, MD bits 0 - 3 enables ALU selection                                                                                                                                                                                            |

|                 |                                     |                                        | U40 pin 1                                                    | With SYSCL, register MD bits 0 - 5                                                                                                                                                                                                         |

| <u> </u>        |                                     |                                        | U27 pin 13                                                   | Primes Acc.                                                                                                                                                                                                                                |

| IRENB           | Instruction register enable         | 2 byte logic<br>U53 pin 6              | Normally high<br>except in 2 byte<br>operation<br>U67 pin 9  | Enables jump selector for a 2 byte operation                                                                                                                                                                                               |

|                 | ,                                   |                                        | U75 pin 1                                                    | Inhibits GENCL during 2 byte operation                                                                                                                                                                                                     |

|                 |                                     |                                        | U20 pins 9, 10<br>U34 pins 9, 10                             | Enables memory data into memory buffer during 2 byte operation                                                                                                                                                                             |

|                 |                                     |                                        | U40 pin 13                                                   | Inhibits writing into S register whilst data is being taken from Mem. buffer during 2 byte operation. Will accept this data on next SYSCL.                                                                                                 |

| IREQ 6          | Interrupt request No. 6             | Interface signal<br>U13 pin 8          | P1A26                                                        | Interrupt request from floppy to computer to read status register. Occurs when int. data bit 1 is set to 1                                                                                                                                 |

| JA = B          | Jump if A = B                       | Instruction register<br>U32 pin 12     | U44 pin 7                                                    | Jump instruction when contents of Acc. equal internal data bits 0 - 7 compared in the ALU                                                                                                                                                  |

| JCARY           | Jump if carry                       | Instruction register<br>U32 pin 15     | U44 pin 6                                                    | Jump instruction as a result of C <sub>n</sub> +8 from combined ALU register                                                                                                                                                               |

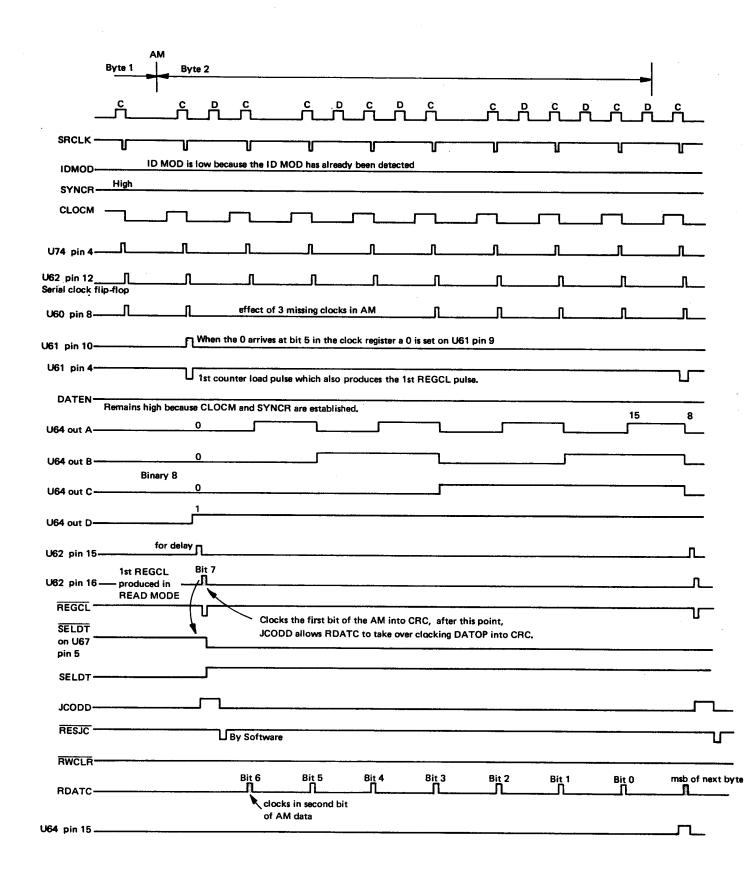

| JCODD           | Jump if command or data is detected | R/w count logic<br>U65 pin 9 (TP 5)    | U44 pin 21                                                   | Jump instruction for every byte of data read<br>or written and including the read AM byte<br>(110) and CRC bytes                                                                                                                           |

| JCOLD           | Jump if command register loaded     | Instruction register<br>U32 pin 19     | U44 pin 4                                                    | Jump instruction when an interface command (37) is loaded into the E register address ABO - 2                                                                                                                                              |

|                 |                                     |                                        | U1 pin 4                                                     | Is low prior to command instruction and enables controlled I/O transfer                                                                                                                                                                    |

| JERGE           | Jump if CRC error                   | R/w logic<br>U68 pin 13                | U44 pin 22                                                   | Jump instruction when the CRC generator<br>indicates an error at the end of a read header<br>or data block                                                                                                                                 |

| JDATRQ          | Jump if data requested              | Interface logic<br>U62 pin 6           | U44 pin 20                                                   | Jump instruction when data is requested from<br>or to main memory during a DMA transfer.<br>Enables data to be transferred at correct time<br>and initiates error if GRANT is not received                                                 |

| KISIML          | Jurno if not index pulse            | Disk interfece<br>U66 pin 7            | U44 pin 18                                                   | Jump instruction when the disk electronics detects that index marker (start of track) has not yet been detected                                                                                                                            |

| J#284J79        | Jump if input register loaded       | Instruction register<br>U32 pin 16     | U44 pin 5                                                    | Jump instruction when address AB0 - 2 and data DB0 - 7 are clocked into the E register                                                                                                                                                     |

| JIRDY           | Junes if not ree-ly                 | Disk interface<br>U56 pin 2            | t I44 pin 2                                                  | Jump instruction when disk is NOT physically able to accept or send data it selected, loaded, uo-to-speed and heads loaded                                                                                                                 |

| SHTRO           | thuse if one track 00               | Disk interface<br>U56 pin 5            | 1 J44 pin 1                                                  | Jump instruction when disk electronics detect that the heads are NOT on track 00                                                                                                                                                           |

| Jannet .        | Assess 60 most comitte protressed   | Disk interform<br>U56 pin 10           | U44 pin 23                                                   | Jump instruction when the disk electronics detect a NOT write protected disk                                                                                                                                                               |

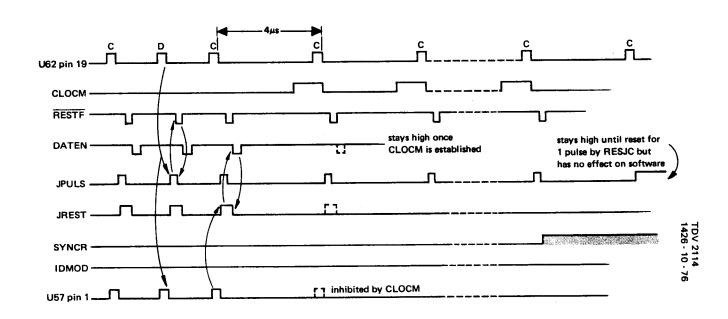

| JPULS           | Jump if data pulse detected         | Read Syncr, logic                      | UA4 pin 3                                                    | Jumo instruction which detects clock pulses from disk to establish SYNCR. (i.e. when 16 JPULS signals occur at 4us intervals after the first CLOCM is established). After SYNCR the JPULS takes no active part in the disk logic sequences |

| APEST           | Jamo reset sync. status             | িnad Syncr. logic<br>াচন pin 10 (TP 4) | U44 Pin 17                                                   | Jump instruction occurring with data/clock pulses from disk at 2µs intervals. Inhibited when CLOCM is established, prior to SYNCR.                                                                                                         |

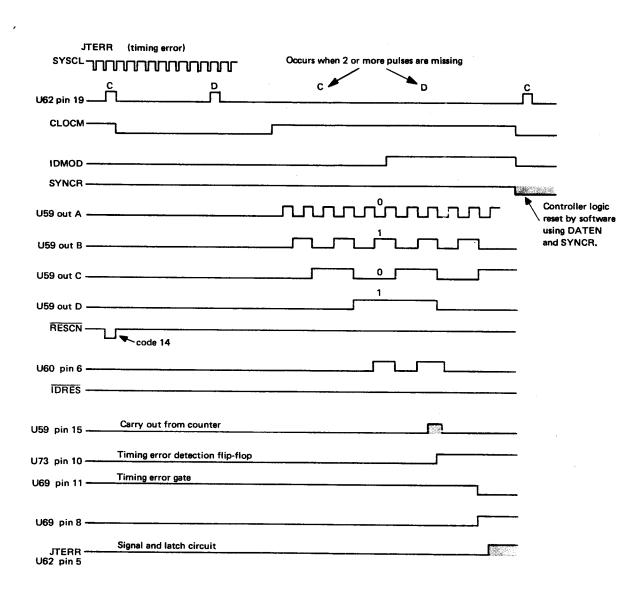

| MERR            | Jump if timing error                | Read timing logic<br>US2 pin 5         | U44 pin 19                                                   | Jump instruction when 2 or more clock pulses<br>are missing other than when looking for the<br>address marker                                                                                                                              |

|                 |                                     |                                        | U77 pin 13                                                   | Feedback line to latch JTERR until software resets the whole read logic                                                                                                                                                                    |

| JN 97032705     | לאמים פישורים                       | Instruction decoder<br>U33 pin 2       | U67 pin 10                                                   | Enables jump selector to load new address int the program counter for 2 byte operation                                                                                                                                                     |

|                 |                                     |                                        |                                                              |                                                                                                                                                                                                                                            |

| Mnemonics          | Signal name                                 | Source                                                   | Destination/s                          | Effect of signal                                                                                                                                                               |  |

|--------------------|---------------------------------------------|----------------------------------------------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LSB                | Least significant bit                       | All registers                                            | Registers and busses                   | Generally as LHS bit on horizontal registers. Generally lowermost bit on vertical registers. (See manufacturers data i.e. Texas, for clarification of position)                |  |

| MBUFF              | Memory buffer enable                        | 2 byte logic<br>U72 pin 9                                | U20 pin 2<br>U34 pin 2                 | Enables output of memory buffer for 2 byte operation                                                                                                                           |  |

|                    |                                             |                                                          | U75 pin 13                             | Causes IRENB signals to go not true during 2 byte operation                                                                                                                    |  |

| M.D. Bits<br>0 - 5 | Memory data bits                            | ALU selection register<br>U19 pins 15, 12<br>10, 7, 5, 2 | U23, U27<br>pins 8,3,4,7,5,6           | Selects ALU functions as shown in 74LS 181<br>Active High Table (Texas)<br>M, S3, S2, C <sub>n</sub> , S1, S0                                                                  |  |

| MIN                | Memory in                                   | Interface signal<br>U11 pin 13                           | P2A15                                  | Signal to computer main memory to place data on general bus during DMA transfer to floppy disk                                                                                 |  |

| MSB                | Most significant bit                        | All registers                                            | Registers and busses                   | General as RHS bit on horizontal registers. Generally uppermost bit on vertical registers. (See manufacturers data i.e. Texas, for clarification of position)                  |  |

| MW                 | Memory write                                | Interface signal<br>U11 pin 11                           | P2A16                                  | Signal to computer main memory to accept data on general bus from floppy disk during a DMA transfer                                                                            |  |

| OSTEN              | Output status enable                        | Interface logic<br>U14 pin 3                             | U7 pin 1                               | Enables the contents of the status register to be placed on the general data bus following an interrupt request to transfer status. Also at the request from the main computer |  |

| OUTPT              | Output                                      | Instruction decoder<br>U33 pin 4                         | U27 pin 4                              | Part of input selection to output decoder (when SEL bit 3 = 0) to produce mp output signals                                                                                    |  |

|                    |                                             |                                                          | U41 pin 4                              | Produces GENCL (when SEL bit 3 = 1) for 1 or 2-byte mp output signals                                                                                                          |  |

|                    |                                             |                                                          | U26 pin 11                             | Enables writing to S register from Acc. or Memory. (When SEL bit 4 = 0)                                                                                                        |  |

| PLOAD              | Program counter load                        | Jump selector<br>U44 pin 10                              | U17 pin 9<br>U31 pin 9                 | Output of jump selector to load the memory data bus into the program counter                                                                                                   |  |

| PSEL 1             | Program select enable                       | Mode decoder<br>U49 pin 2                                | U29 pin 19<br>U15 pin 19               | Enables addressing from locations 0 to 511 in the read only memory as shown in the PSEL 2 table                                                                                |  |

| PSEL 2             | Program select enable Program select enable | Mode decoder<br>U49 pin 6<br>Mode decoder                | U29 pin 15<br>U53 pin 11<br>U15 pin 15 | Enables addressing to a specific part of the read only programmed memory. With a COMCL operation, DB0 (PSEL 1) is used with DB2 (PSEL 2) to extend the addressing from         |  |

| PSEL 2             | Program select eneme                        | U53 pin 10                                               |                                        | DE (1 1023)  PSEL 1 PSEL 2 ADD CHIP (DB0) (DB2)  0 0 0 - 255 U29 1 0 256-511 U29 0 1 512-767 U15 1 768-1023 U15                                                                |  |

| RCMDIS             | Read clock mode disable                     | Mode decoder<br>U49 pin 9                                | U72 pin 1                              | Resets read data input enable signal to CLOCM counter                                                                                                                          |  |

|                    |                                             | 043 p 3                                                  | U71 pin 1                              | Resets clock mode counter (CLOCM). Produced as a result of a Syncr. fault.                                                                                                     |  |

| RCREN              | Read clock register enable                  | Input decoder<br>U38 pin 6                               | U46 pin 1                              | Enables the data in the parallel read register to be clocked on to the internal data bus and transferred to the Acc. Occurs when JCODD is detected by software                 |  |

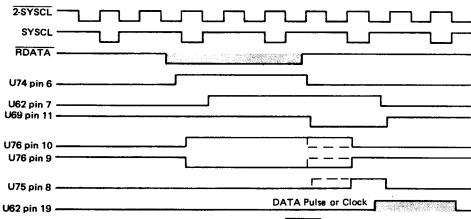

| RDATA              | Read data                                   | Disc interface<br>JF pin 5                               | U69 pin 13<br>U74 pin 5                | Raw data from disk is synchronised with<br>SYSCL and either stretched or shortened to<br>a standard 200ms pulse width                                                          |  |

|                    |                                             | •<br>•                                                   | R6                                     | Pull-up resistor for TTL compatibility and correct matching                                                                                                                    |  |

| RDATC              | Read data clock                             | Read logic<br>U60 pin 12                                 | U63 pin 5                              | Produces a position pulse for every clock pulse being read. Allows counter to count only at this time                                                                          |  |

|                    |                                             |                                                          | U62 pin 3                              | Produces clock pulses to clock CRC generator for every data bit (DATOP)                                                                                                        |  |

| RDREN              | Read data register enable                   | Input decoder<br>U38 pin 7                               | U50 pin 1                              | Enables the data in the parallel read register to be clocked on to the internal data bus and transferred to the Acc. Occurs when JCODD is detected by software                 |  |

| READY              | Floppy disk ready (see JRDY)                | Disk interface<br>JF pin 29                              | U56 pin 3                              | Causes jump instruction (see JNRDY)                                                                                                                                            |  |

|                    |                                             |                                                          |                                        |                                                                                                                                                                                |  |

| Mnemonics | Signal name               | Source                           | Destination/s                       | Effect of signal                                                                                                                                                                                                                                                                                                                             |  |

|-----------|---------------------------|----------------------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

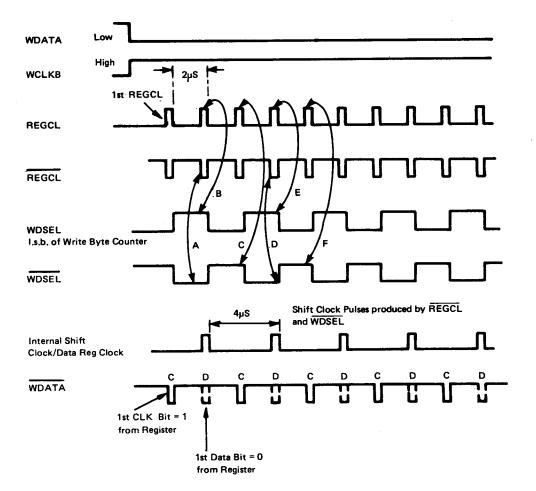

| REGCL     | . Register clock          | R/W logic<br>U62 pin 16          | U52 pin 11<br>U52 pin 13            | Clocks data and clock alternately every 2µs when writing on to disk. R/W counter produces pulses every 2µs by counting SYSCL pulses from 6 to 15 cyclically.                                                                                                                                                                                 |  |

|           |                           |                                  | U65 pin 11 (TP5)                    | Sets JCODD on the next SYSCL following the SYSCL which caused the counter to output (pin 15) after receiving 8 clock pulses when reading                                                                                                                                                                                                     |  |

|           |                           |                                  | U66 pin 4                           | Produces CRCE clock pulse when writing.<br>Inhibited on alternate pulses by WDSEL, to<br>clock only at 4µs intervals                                                                                                                                                                                                                         |  |

| REGCL     | Register clock            | R/W logic<br>U53 pin 2           | U54 pin 2                           | When writing, clocks 16 pulses into counter to indicate that 1 byte of WRITE information has been written (1 byte MODE = 8 CKS + 8 DATA)                                                                                                                                                                                                     |  |

|           |                           |                                  | U46 pin 11<br>U50 pin 11            | After 8 clock pulses (1 byte), clocks the serial clocks/data from the READ serial read to the parallel read MODE registers                                                                                                                                                                                                                   |  |

|           |                           |                                  | U47 pin 2<br>U48 pin 2              | When writing, clocks the previously loaded parallel data, serially out of the write clock and data registers. WRITE Clocks out every 4µs since WDSEL MODE alternately inhibits the REGCL (from U54)                                                                                                                                          |  |

|           |                           |                                  | U65 pin 3                           | Sets the SELDT bistable when AM is detected when reading. Disabled by MODE when writing                                                                                                                                                                                                                                                      |  |

| RESCN     | Reset counter             | Read decoder<br>U57 pin 7        | U59 pins 9, 10                      | After the start of CLOCM pulses this signal resets ID counter to zero after nominally 8 SYSCL except when a clock pulse fails to appear in sync mode and clock mode. (Start of ID detection or possible JTERR).                                                                                                                              |  |

| RESDI     | Reset data input          | R1/R2 decoder<br>U38 pin 9       | U12 pin 12                          | Resets the input address register AB0-2 from computer. Results from JCOLD or JINLD instructing program to set busy status and reset input. Byte 2 in GENCL organises status transfer and reset signals                                                                                                                                       |  |

| RESJC     | Reset JCODD               | R1/R2 decoder<br>U38 pin 11      | U66 pin 10                          | Resets JCODD immediately the software detects that JCODD has been set. Occurs after each JPULS during synchronisation, on detection of AM byte and after each byte read or written                                                                                                                                                           |  |

| RESTF     | TF Reset status flip-flop | JCODD logic<br>U66 pin 8         | U65 pin 13                          | Produced by RESJC to reset the JCODD bistable                                                                                                                                                                                                                                                                                                |  |

|           |                           |                                  | U58 pin 1                           | Resets JPULS until SYNCR is established and thereafter each time JCODD is detected. Setting or resetting the JPULS after SYNCR has no significance and is ignored by the software                                                                                                                                                            |  |

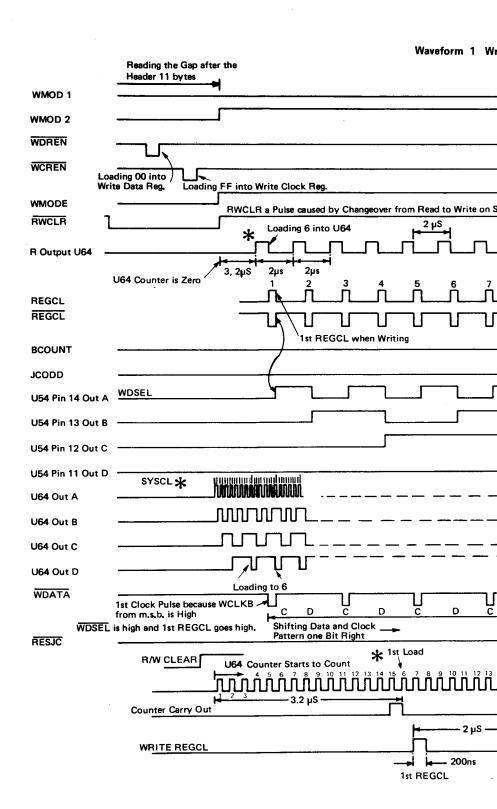

| RWCLR     | Read/write clear          | R/W logic<br>U63 pin 3           | U64 pin 1                           | Occurs when write mode is initiated from a JCODD count after the 11th byte following the header and at the start of the 6 byte syncr. gap. Also occurs for synch, fault or any read fault                                                                                                                                                    |  |

|           |                           |                                  | U62 pin 1<br>U65 pin 1<br>U66 pin 9 | Resets bistables in RDATA logic, R clock logic, REGCL line and RDATC logic. Resets JCODD and SELDT bistables and JPULS via RESTF                                                                                                                                                                                                             |  |

| 2 BYTE    | Second byte               | Instruction decoder<br>U33 pin 1 | U72 pin 14                          | Decoded when an m.p. instruction code requires data or address information to be transferred on the internal data and address busses                                                                                                                                                                                                         |  |

|           |                           |                                  | U74 pin 1                           | Inversion to U75 pin 13 input to allow 'toggle' or 'no-change' of bistable                                                                                                                                                                                                                                                                   |  |

|           |                           |                                  | U75 pin 12                          | With output of U75, inhibits the IRENB signals during 2 byte operation                                                                                                                                                                                                                                                                       |  |

| 7 CENB    | Seven count enable        | Mode decoder<br>U49 pin 5        | U64 pin 3                           | Initiated by software when the JCODD is set by the REGCL which resets the R/W counter to count in the 2nd byte of the CRC control byte. The R/W counter is preset to 1001(9). After 7 more RDATC pulses the REGCL is set and sets JCODD which informs the software that the complete CRC control word has been clocked into the CRC checker. |  |

|           |                           |                                  |                                     |                                                                                                                                                                                                                                                                                                                                              |  |

| Mnemonics | Signal name                                 | Source                           | Destination/s                                                                     | Effect of signal                                                                                                                                                                                                                                                                                                                                                                           |

|-----------|---------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SEBEN     | Scratch pad- and E-registers enable         | instruction decoder<br>U33 pin 3 | U18 pins 1, 2                                                                     | Enables the instruction selection register to<br>address the S register, for single bytes only,<br>during E to S transfers of disk commands and<br>initial addressing                                                                                                                                                                                                                      |

| SEBEN     | Scratch pad- and E-registers enable         | Instruction decoder<br>U77 pin 8 | U28 pin 1                                                                         | Allows add, and data from E reg. to be clocked in S. register (SEL bit 4 = 0)                                                                                                                                                                                                                                                                                                              |

| ·         |                                             |                                  | U8 pin 1                                                                          | Enables E reg. contents to be placed on to internal data bus for transfer to S reg.                                                                                                                                                                                                                                                                                                        |

|           |                                             |                                  | U11 pin 1                                                                         | Enables E reg. (ADDRESS) contents to be placed on int. add. bus to S reg.                                                                                                                                                                                                                                                                                                                  |

| SELB 0    | Instruction selection register bit 0        | Instruction selection register   | U44 pin 15                                                                        | Part of address selection C0 - C3 for jump instructions                                                                                                                                                                                                                                                                                                                                    |

|           |                                             | U18 pin 3                        | U39 pin 1                                                                         | Part of input selection for output decoder                                                                                                                                                                                                                                                                                                                                                 |

|           |                                             |                                  | U38 pin 2                                                                         | Part of input selection for input decoder                                                                                                                                                                                                                                                                                                                                                  |

|           |                                             |                                  | U21 pin 3<br>U35 pin 3                                                            | Part of address selection for S register                                                                                                                                                                                                                                                                                                                                                   |

| SELB 3    | Instruction selection register bit 3        | Instruction selection register   | U33 pin 14                                                                        | Part of instruction decoder                                                                                                                                                                                                                                                                                                                                                                |

|           |                                             | U18 pin 6                        | U44 pin 11                                                                        | as bit 0 (pin 15)                                                                                                                                                                                                                                                                                                                                                                          |

|           |                                             |                                  | U27 pin 5<br>U40 pin 9                                                            | Part of input selection for output decoder and GENCL logic                                                                                                                                                                                                                                                                                                                                 |

|           |                                             |                                  | U21 pin 6<br>U35 pin 6                                                            | As bit 0 (pin 3)                                                                                                                                                                                                                                                                                                                                                                           |

| SELB 4    | Instruction selection register bit 4        | Instruction selection register   | U33 pin 13                                                                        | As bit 3                                                                                                                                                                                                                                                                                                                                                                                   |

|           |                                             | U32 pin 9                        | U75 pin 2                                                                         | Part of input to output decoder and selection<br>of GENCL logic                                                                                                                                                                                                                                                                                                                            |

|           |                                             |                                  | U38 pin 3                                                                         | As bit 0 (pin 2)                                                                                                                                                                                                                                                                                                                                                                           |

|           |                                             |                                  | U27 pins 9, 2                                                                     | Selects either write or read enabling signals<br>for the S register                                                                                                                                                                                                                                                                                                                        |

| SELB 1, 2 | Instruction selection register bits 1 and 2 | Instruction selection register   | U44 pins 14, 13                                                                   | As bit 0 (pin 15)                                                                                                                                                                                                                                                                                                                                                                          |

|           | oris i and 2                                | U18 pins 4, 5                    | U39 pins 2, 3                                                                     | As bit 0 (pin 1)                                                                                                                                                                                                                                                                                                                                                                           |